icore4tx_fpga_23

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-06-29 | gingko | 初次建立 |

实验二十三:Slave Serial模式配置FPGA

一、实验目的与意义

- 了解Xilinx FPGA的配置模式。

- 学习Xilinx FPGA的Slave Serial配置模式原理。

- 掌握Xilinx FPGA的Slave Serial配置模式过程。

二、实验设备及平台

- iCore4TX 双核心板点击购买。

- J-link(或相同功能)的仿真器。

- Micro USB线缆。

- 装有Keil开发软件的平台。

三、实验原理

- iCore4TX双核心板是ARM+FPGA架构。板卡上设计有JTAG接口,用于FPGA的调试和程序的烧写。由于FPGA掉电后程序易丢失的特性,可以采用Slave Serial Mode配置FPGA。此模式中,FPGA作为被动配置器件,ARM作为主控器件,控制配置时序,将存储于非易失性存储器的配置文件配置到FPGA内部,从而使FPGA每次上电后保持原有功能。

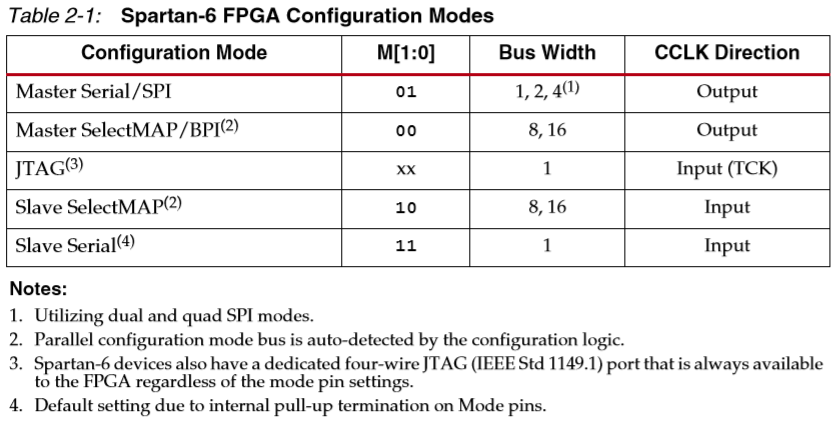

- 通过查阅FPGA手册可以了解到SPARTAN-6 FPGA的配置模式有5种,这5种配置模式是由M[1:0]的组合电平决定的,如下表所示:

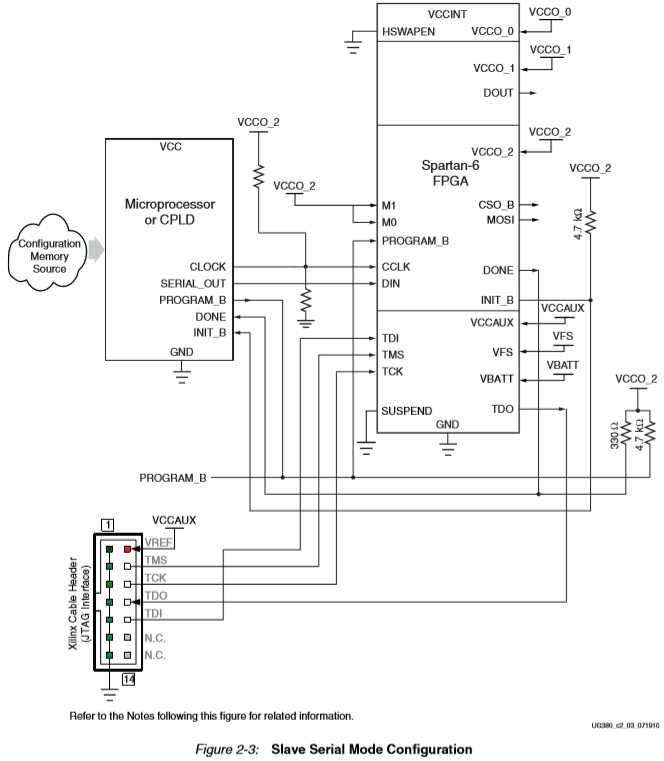

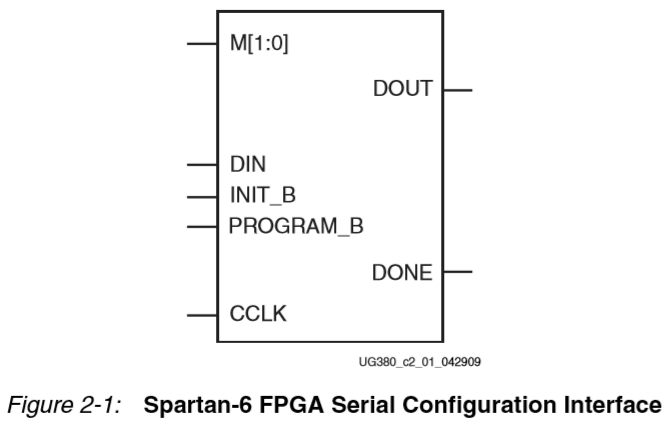

- iCore4TX则采用Slave Serial模式配置FPGA,此方式是由ARM控制配置时序和读取配置文件并配置到FPGA种,好处是可以发挥iCore4TX的ARM+FPGA架构的优势,且配置文件可以存储到不同类型的非易失存储器中,较为灵活。那么Slave Serial配置模式下,ARM和FPGA之间的信号连线是什么样的呢,可以参考官方设计,如图所示:

Slave Serial模式下FPGA信号线如23-3中所示,各信号定义参考图23-4表格。

Slave Serial模式下FPGA信号线如23-3中所示,各信号定义参考图23-4表格。

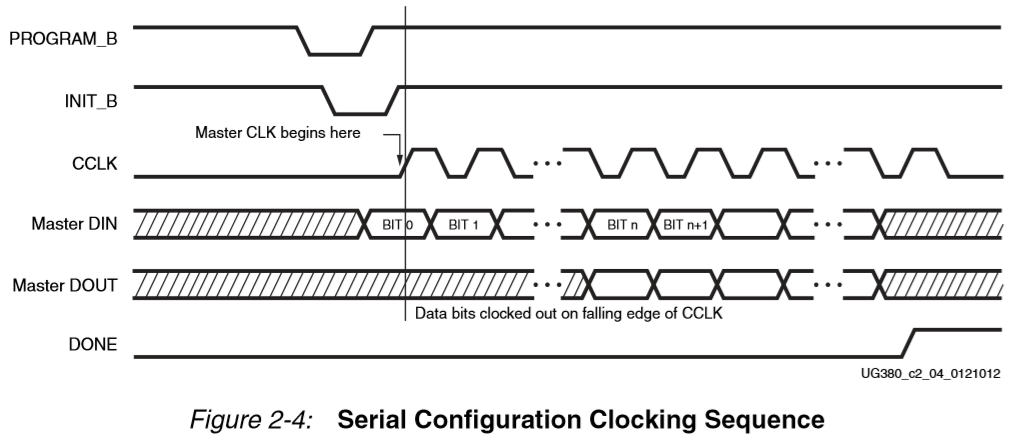

明白了这几个信号的含义,再来看一下PS配置模式的时序图:

明白了这几个信号的含义,再来看一下PS配置模式的时序图:

- 注意:Bit0是第一个字节的高位,例如,如果发送的第一个字节为0xAA(1010_1010),bit0=1,bit1=0,bit2=1,…。

- 从时序图中也可以看到,整个配置过程大致如下:

- 1)PROGRAM_B首先拉低一个时钟周期,在信号的上升沿开始进行配置;

- 2)可以通过拉低INIT_B信号延迟开始FPGA的slave Serial mode 配置;

- 3)ARM 芯片输出DCLK和DATA开始传输信号,保证时钟信号的上升沿在数据的稳定期;

- 4)待配置完成后DONE被拉高,表示配置完成。

2.生成配置文件

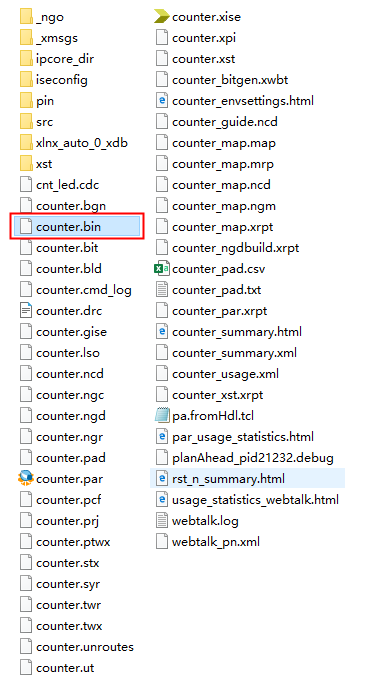

- Slave Seial Mode下的配置文件是通过ISE软件生成的.bin格式的文件。将生成的.bin文件存储到SD卡或者U盘等非易失性存储器,然后通过STM32配置到FPGA中。ISE14.7软件生成.bin格式文件的流程如下:

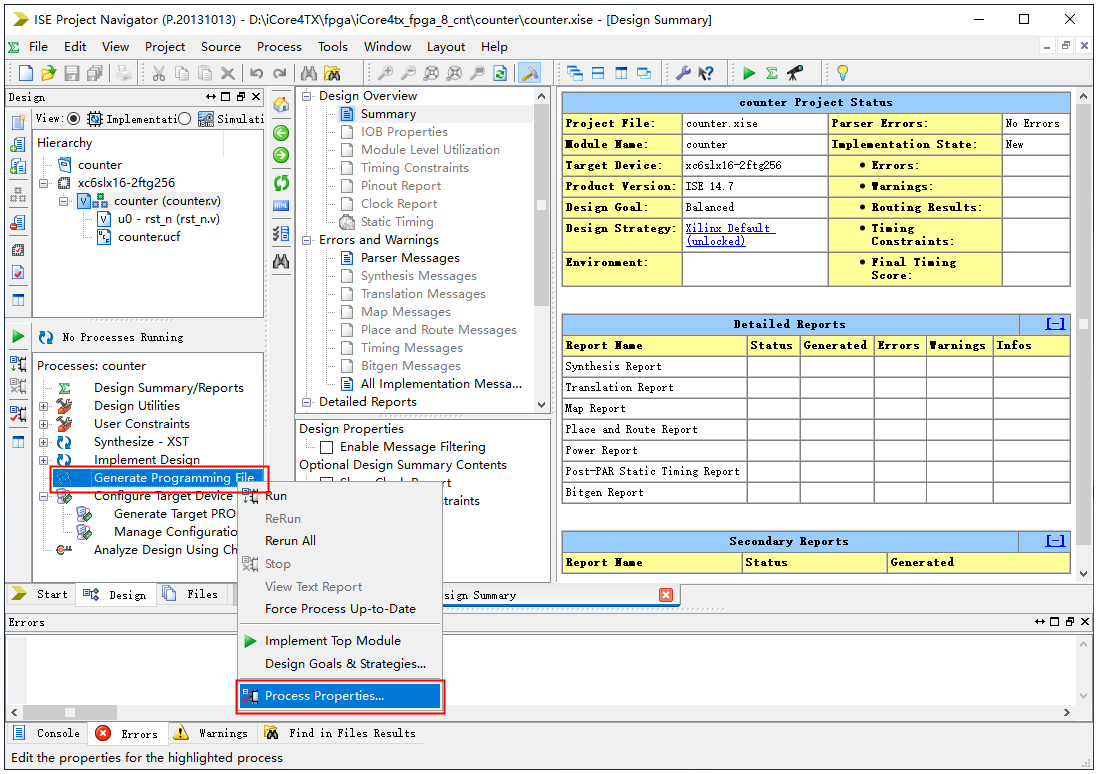

1、打开ISE工程,以实验八工程为例,右键点击Generate Programming FileProcess Properties…。

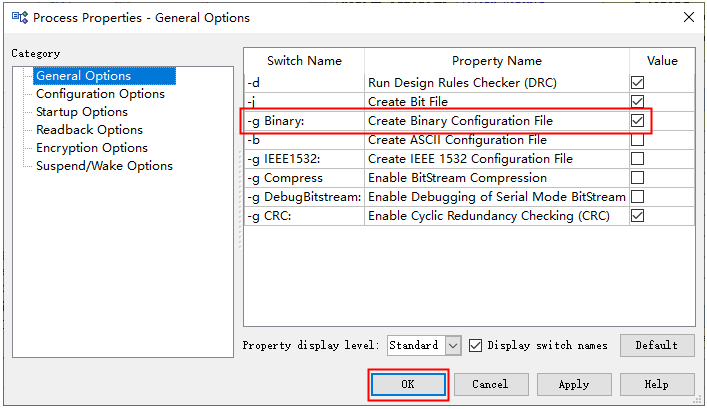

2、找到 -g Binary: 行后面的Value,并打勾;选中次项的功能是创建Binary 格式配置文件。然后点击OK。

2、找到 -g Binary: 行后面的Value,并打勾;选中次项的功能是创建Binary 格式配置文件。然后点击OK。

3、返回工程界面后重新编译,即可生成配置的.bin文件。

3、返回工程界面后重新编译,即可生成配置的.bin文件。

四、操作步骤:

- 1、将例程中FPGA升级文件夹下的.bin文件拷贝进SD卡system文件夹下;

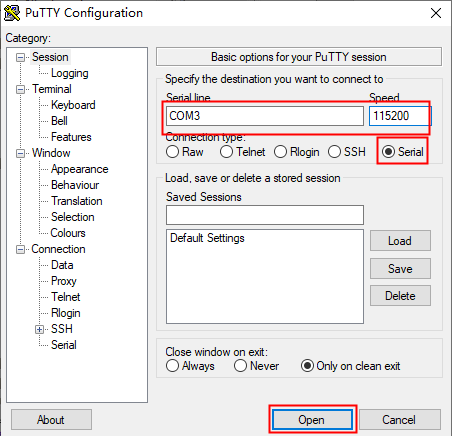

- 2、打开PuTTy串口终端软件,选择Serial,修改COM口端号(设备管理器里查看),修改波特率和代码中一致,点击Open;

- 3、连接仿真器和iCore4TX双核心板,并通过Micro USB线给板子供电;

- 4、烧写ARM程序到iCore4TX双核心板的ARM芯片;

- 5、下载完成后重新上电。

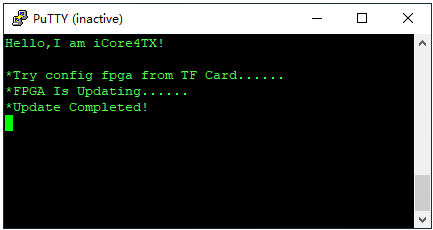

五、实验现象:

icore4tx_fpga_23.txt · 最后更改: 2022/04/01 11:39 由 sean