icore4tfpga21

目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-03-09 | gingko | 初次建立 |

实验二十一:双口RAM实验——基于双口RAM的ARM与FPGA通信

一、 实验目的与意义

- 掌握双口RAM IP核的调用及例化方法。

- 掌握RAM读写时序。

- 掌握QuartusII的使用方法。

二、 实验设备及平台

- iCore4T 双核心板。

- iTool A(或相同功能)仿真器。

- USB Type C 线缆。

- Keil MDK 开发平台。

- Quartus开发平台。

- 电脑一台。

三、 实验原理

- RAM全称是Random Access Memory(随机存取存储器),是与处理器进行数据交互的存储器。既可向指定地址单元写入信息也可从指定地址单元中读取信息,掉电后数据丢失,属于易失性存储器。

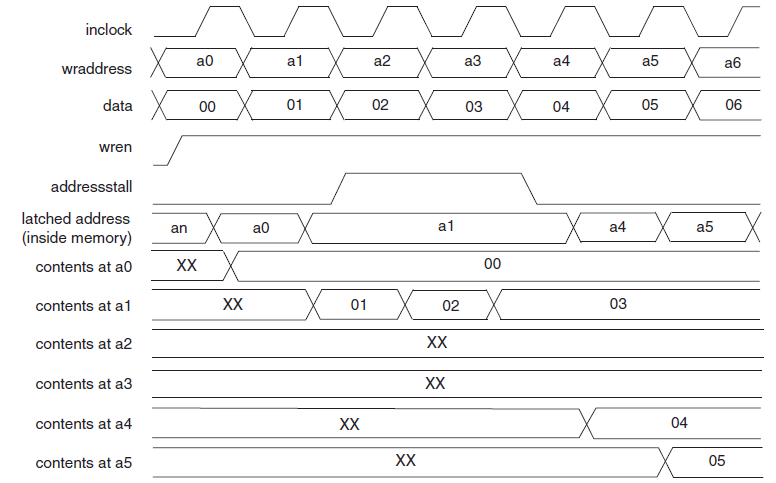

- 双口RAM分为伪双口RAM和真双口RAM两种,伪双口RAM一个端口只读,另一个端口只写;而真双口RAM两个端口都能读写。从整体上讲,真双口RAM和伪双口RAM都能同时进行读写操作;双口RAM虽然有两个端口,两套数据线和地址线,但是存储数据的空间单元是共享的,因此存储后的数据也是共享的。本实验中通过例化IP核在FPGA内部构建真双口RAM存储器,其基本工作时序和普通RAM一致,都是以时钟上升沿作为触发事件,在上升沿到来前保证地址和数据稳定即可将数据准确的写入对应的地址单元中,读取时,也是如此。其读写时序如图21.1所示。

- 本实验基于ARM+FPGA构架,通过SPI实现ARM与FPGA之间通信,以双口RAM作为FPGA内部的数据存储器,实现ARM对数据的读写功能。ARM通过SPI将数据发送到FPGA,FPGA通过A端口将数据写入存储器中,然后通过B端口读出来返回给ARM,实现数据的交互。实验流程较为简单,重点是要掌握双口RAM的读写操作时序以及双口RAM IP核的调用。

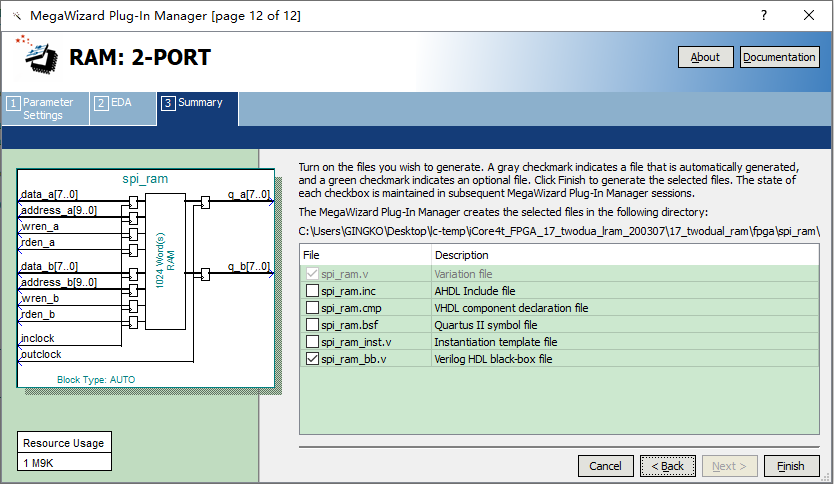

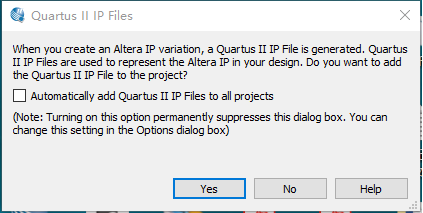

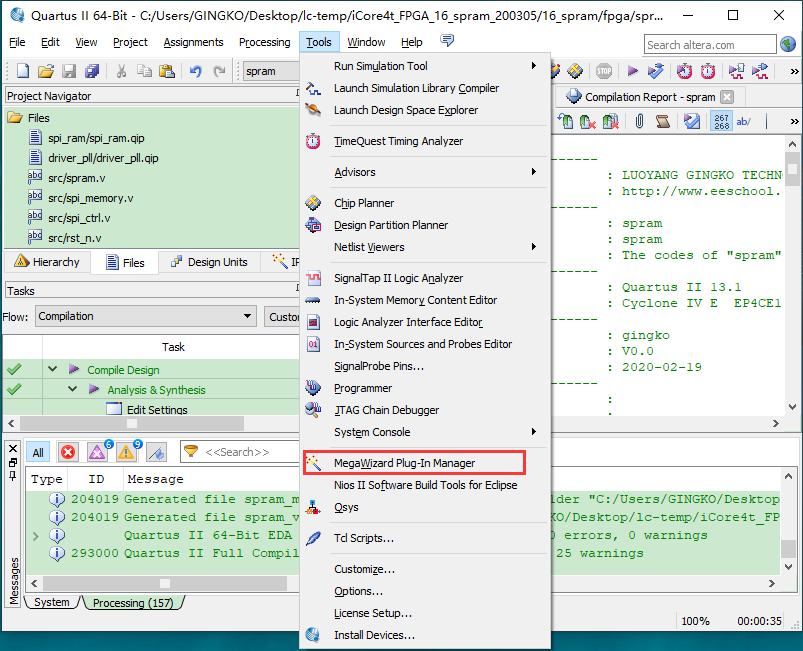

四、 RAM IP核调用

1、新建一个工程名为pll的工程,然后点击Tool →Megawizard Plug-In Manager,如图21.2所示。

2、在下面界面中保持默认,直接Next即可,如图21.3所示。

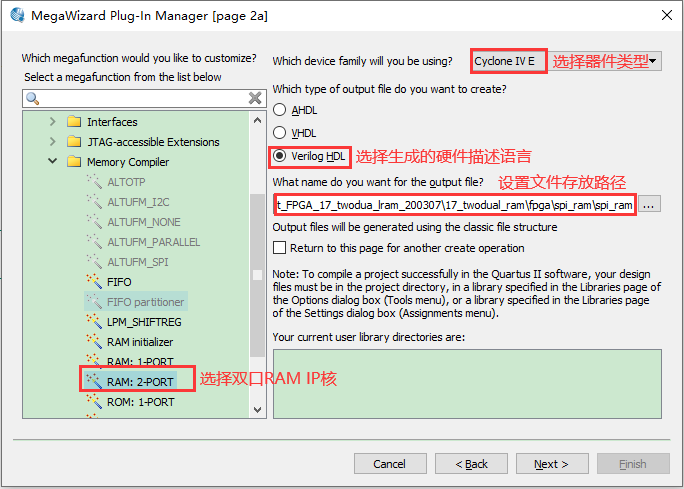

3、在该界面中选择双口RAM IP核、芯片类型、硬件描述语言类型及IP核相关文件存储位置,如图21.4所示。

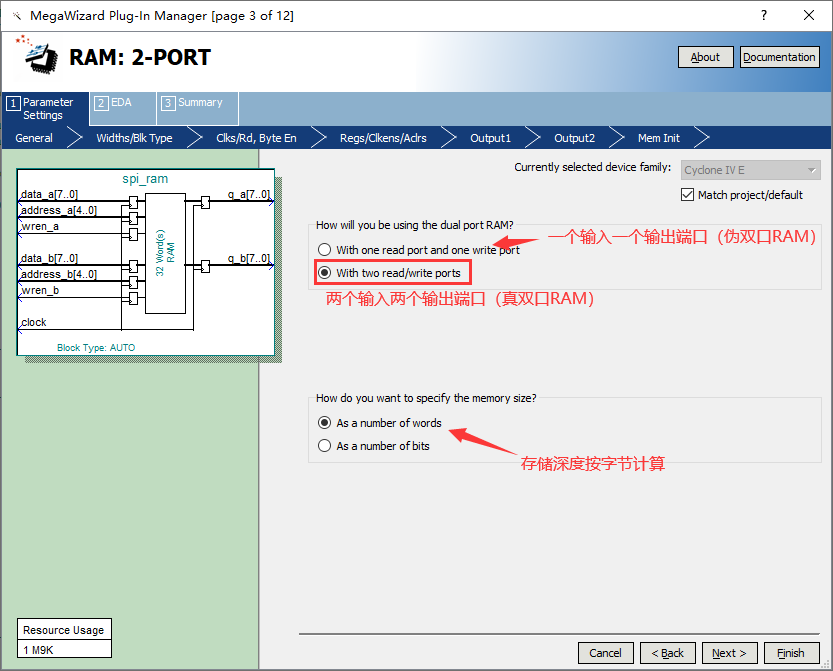

4、在该对话框中选择真双口RAM(两个输入两个输出),存储深度以字节为单位,如图21.5所示。

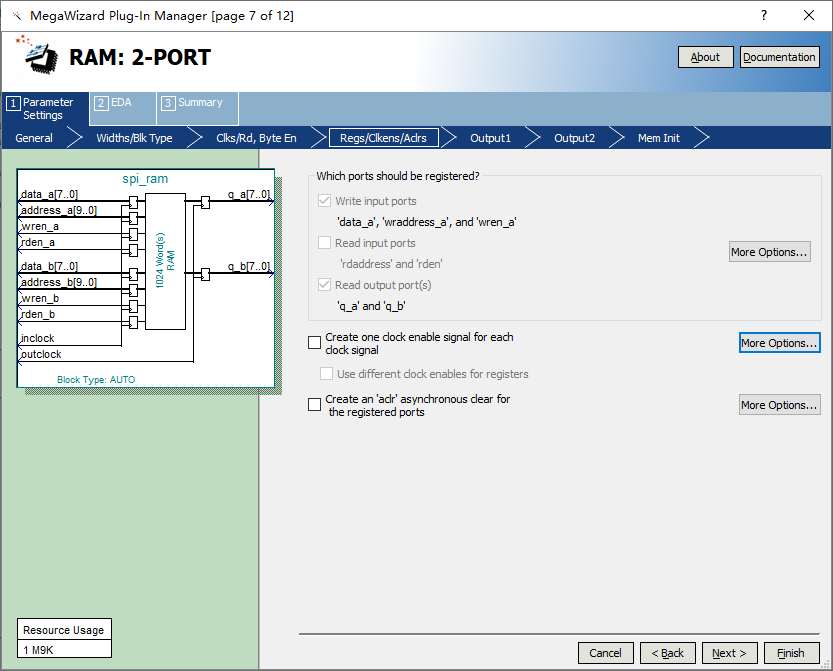

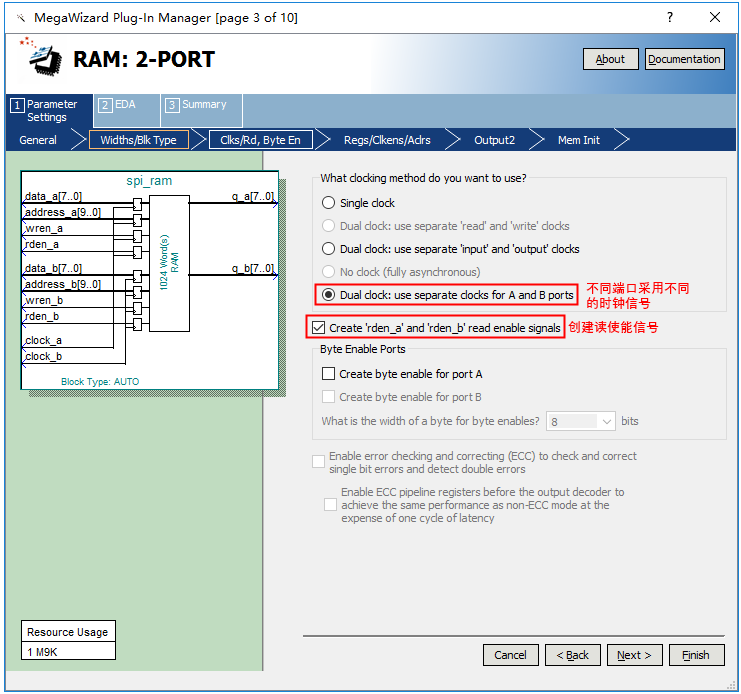

6、在此对话框选择时钟信号输入方式、增加读使能信号,如图21.7所示。

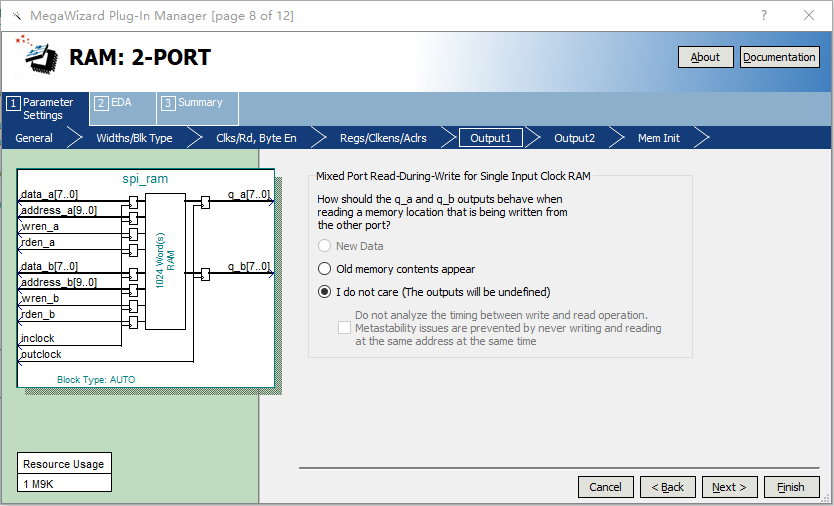

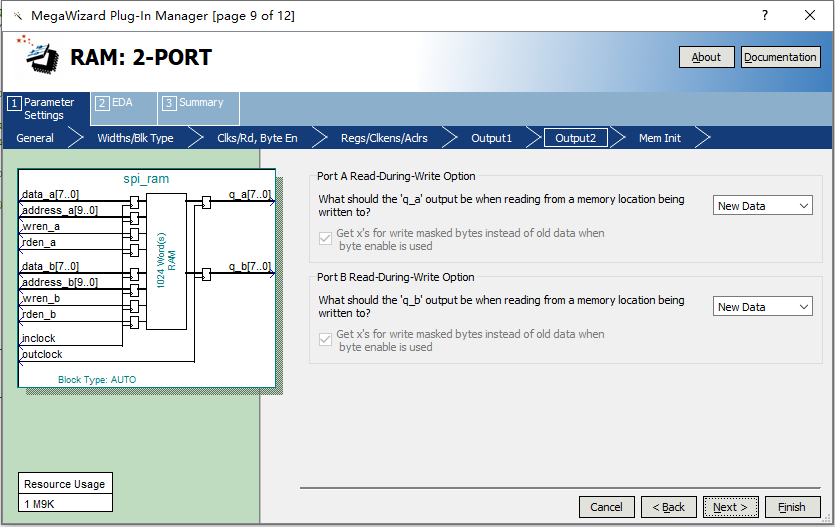

9、选择读出的数据是新数据还是老数据,一般设置新数据(New Data),如图21.10所示。

五、 代码讲解

- IP核调用只是生成相关的模块文件,在应用中要实现存储、读写功能,还需要对IP核进行实例化操作,双口RAM IP核例化代码如下:

//------------------------------------------------// //spi_ram //负责存储SPI通信的数据(具体的存储位置可通过spi命令寄存器设置) //双口RAM的缺点是与单口RAM相比,相同容量的RAM占用逻辑资源比较多。 //优点在于具有2个输入2个输出端口,两个端口都可用于输入输出,可实现同时读写,便于控制。 //数据从A端口写入,从B端口读出 wire [7:0]b_dataout; wire [7:0]a_dataout; spi_ram u0( .address_a(a_addr), .address_b(address_b), .data_a(a_datain), .data_b(b_datain), .clock_a(!a_clk), .clock_b(b_clk), .rden_a(a_rden), .rden_b(b_rd_en), .wren_a(a_wren), .wren_b(1'd0),//b_wr_en .q_a(a_dataout), .q_b(b_dataout) );

六、 实验步骤及实验结果

- 1、将硬件正确连接,如图21.15所示。

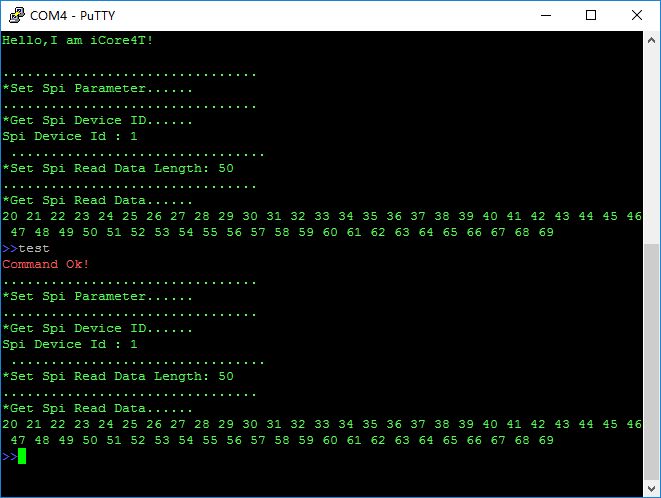

- 2、打开putty串口调试工具,打开设备管理器查看对应的端口信息,在putty中打开对应的端口,用于打印串口信息及控制RAM读写;

- 3、将编写好的FPGA代码进行编译,并下载到开发板中;

- 4、将编写好的ARM代码编译,并下载到开发板中,putty工具中会打印相应的SPI通信相关信息(若想多次测试,查看结果在putty中输入“test”即可);

- 5、观察实验现象及putty终端打印信息——FPGA_LED闪烁,putty终端打印如图21.16所示.

七、 拓展实验

1.通过Signaltap观察RAM读写时序是否和参考时序一致。

icore4tfpga21.txt · 最后更改: 2024/04/10 11:27 由 zhaowenzhe