目录

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-11-19 | zgf | 初次建立 |

实验七:锁相环实验——锁相环IP核调用

一、 实验目的与意义

- 掌握锁相环IP核的使用方法。

- 掌握HqFpga的使用方法。

二、 实验设备及平台

- iCore3L 双核心板。

- XiST USB Cable(或相同功能)仿真器。

- Micro USB线缆。

- 装有HqFpga开发软件的电脑一台。

三、 实验原理

- 锁相环全称是锁相环路,是一种反馈控制电路,其主要特点是利用外部输入的参考信号控制环路内部振荡信号和相位。锁相环通常由鉴相器、环路滤波器和压控震荡器三部分组成。

- 通过HqFpga软件配置FPGA可以调用内部IP核资源,通过改变IP核内部分频、倍频及相位差等参数,改变PLL IP核的输出频率和相位,从而产生用户所需要的时钟信号。

- 本实验工程通过HqFpga软件调用PLL IP核,并对其参数进行配置,从而利用FPGA产生不同频率的输出信号;将不同的输出信号映射到FPGA引脚,可以通过示波器等设备查看PLL输出信号的波形,也可以通过HqFpga软件的调试模式查看输出信号的变化。

四、 实验步骤及结果

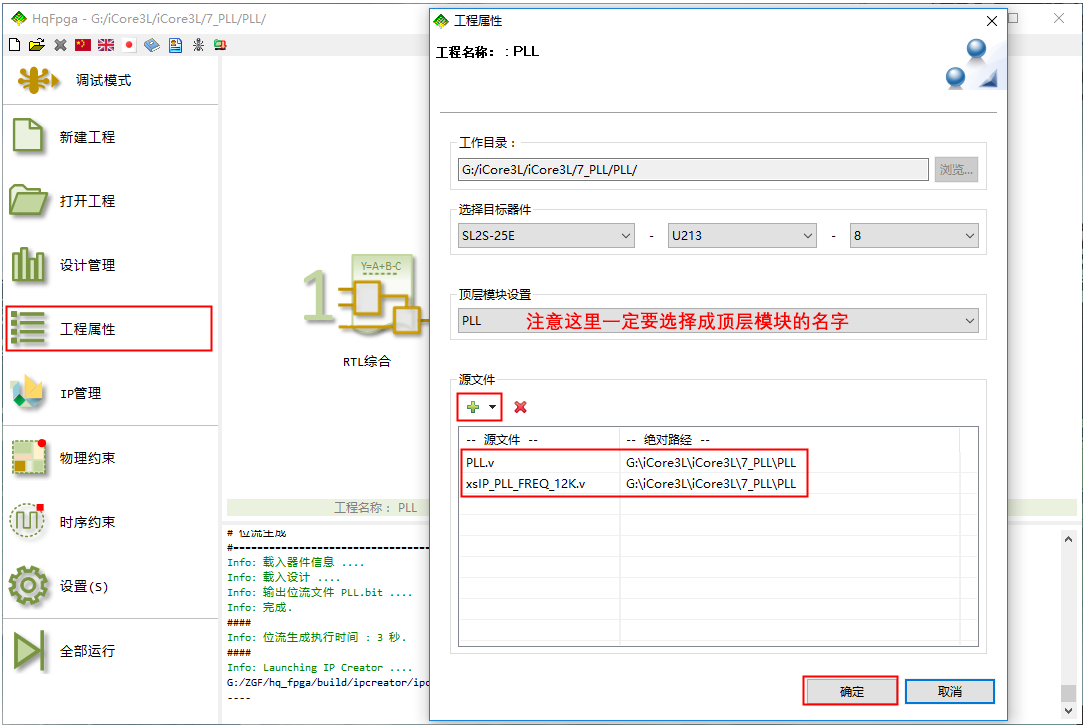

一、建立工程

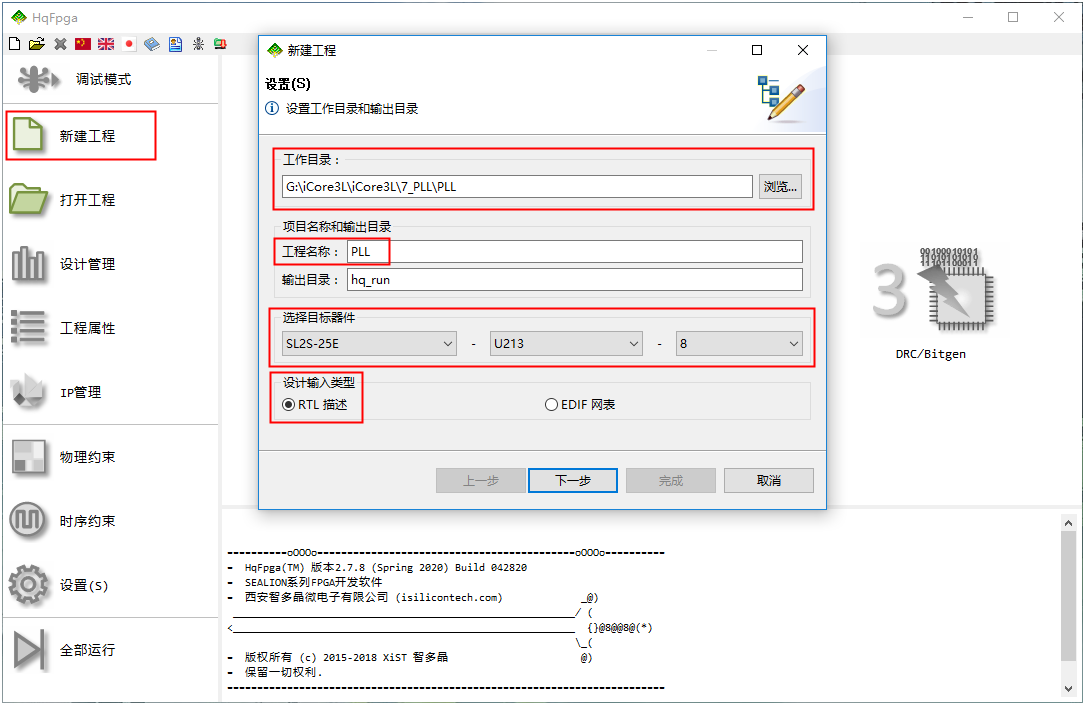

1、新建工程,工程名设置为PLL;打开HqFpga软件,点击左侧边栏的“新建工程”按钮,在弹出窗口中设置好保存路径和工程名称;目标器件选择SL2S-25E-8U213C,设计输入类型选择RTL描述。点击“下一步”,弹出的“RTL输入:”界面直接点击“完成”按钮。

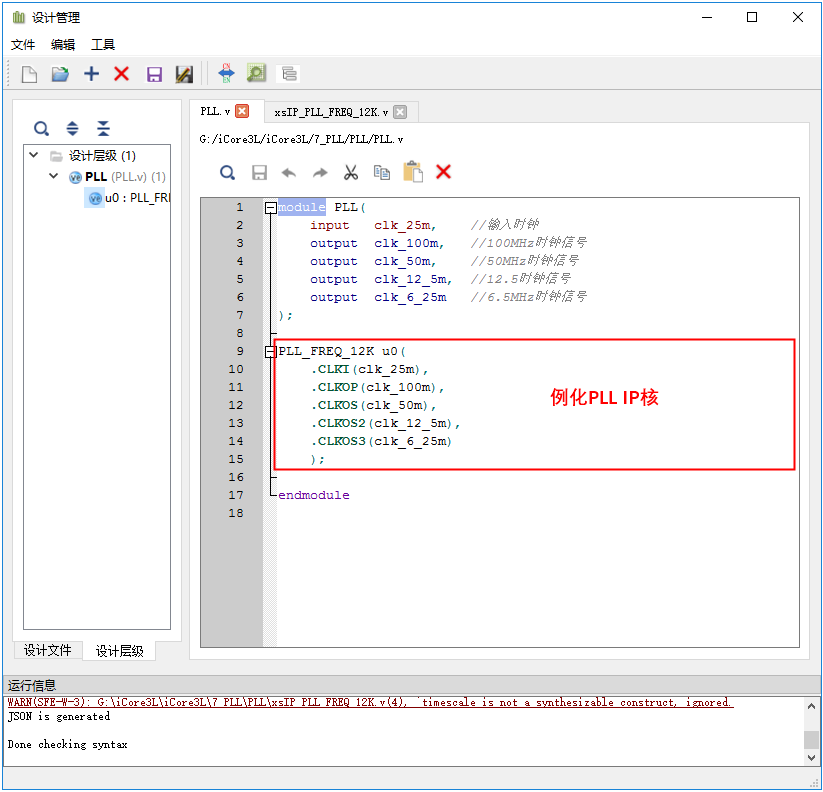

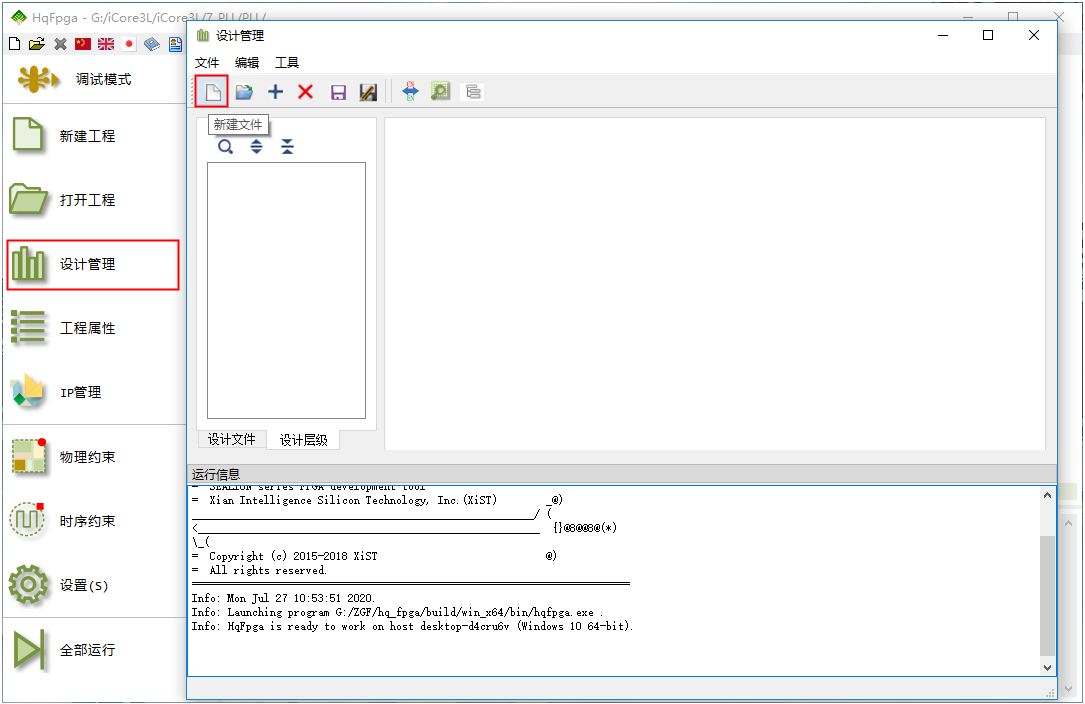

2、点击左侧栏的“设计管理”按钮,弹出窗口中点击“新建文件”按钮,建立顶层文件。

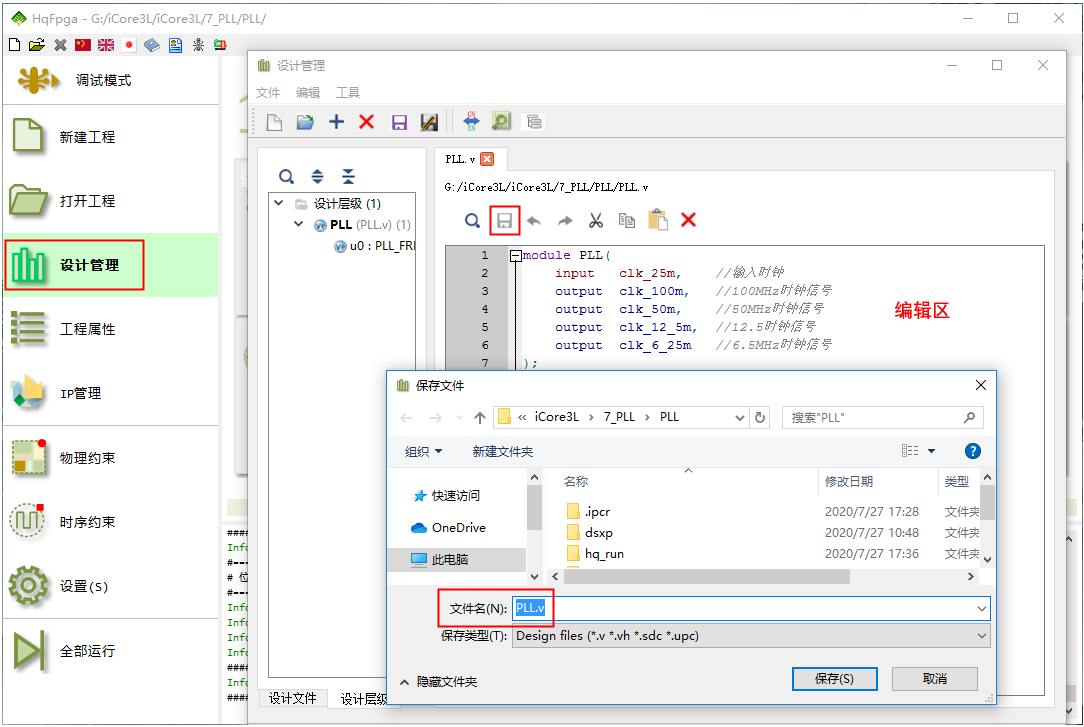

3、在编辑区输入顶层文件代码,然后点击保存,弹出的“保存文件”窗口中给文件命名,本例程中命名为PLL.v,完成顶层文件的建立。

二、调用PLL IP核

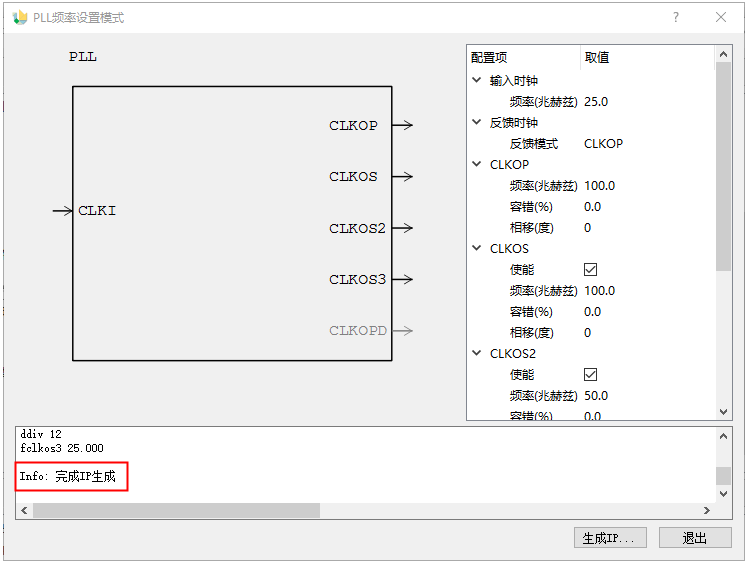

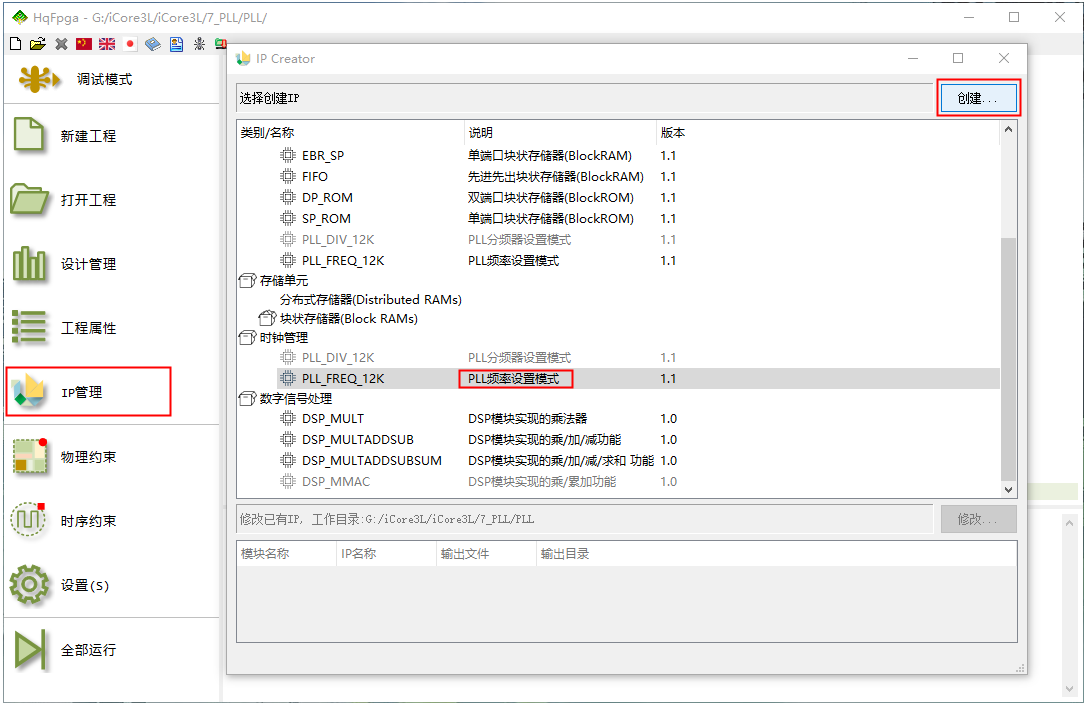

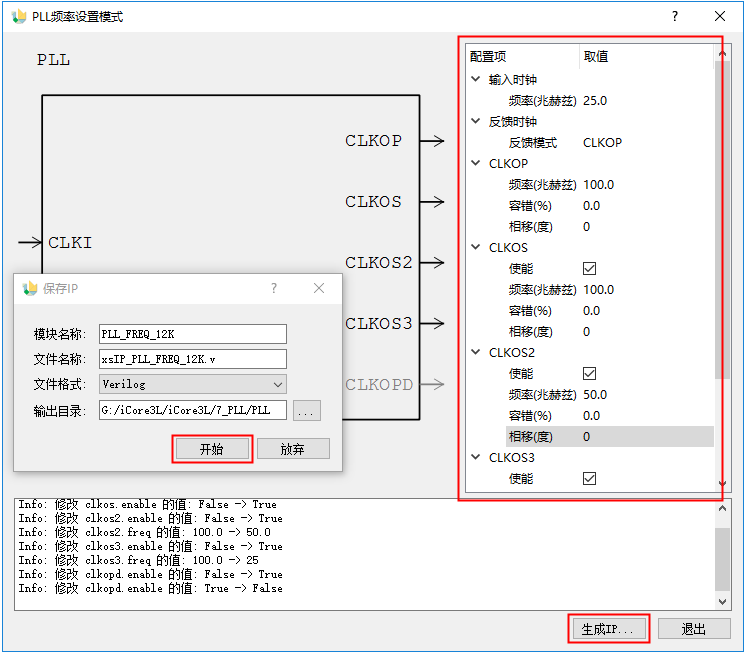

1、点击左侧栏的“IP管理”按钮,找到“PLL频率设置模式”,然后点击右上角的

“创建”按钮。

2、弹出的PLL频率设置窗口中,在右侧分别设置好输出时钟的频率和相位等信息。待4个输出时钟设置完,点击右下方的“生成IP…”按钮,并点击“开始”按钮。

三、通过HqFpga软件“调试模式”查看输出波形

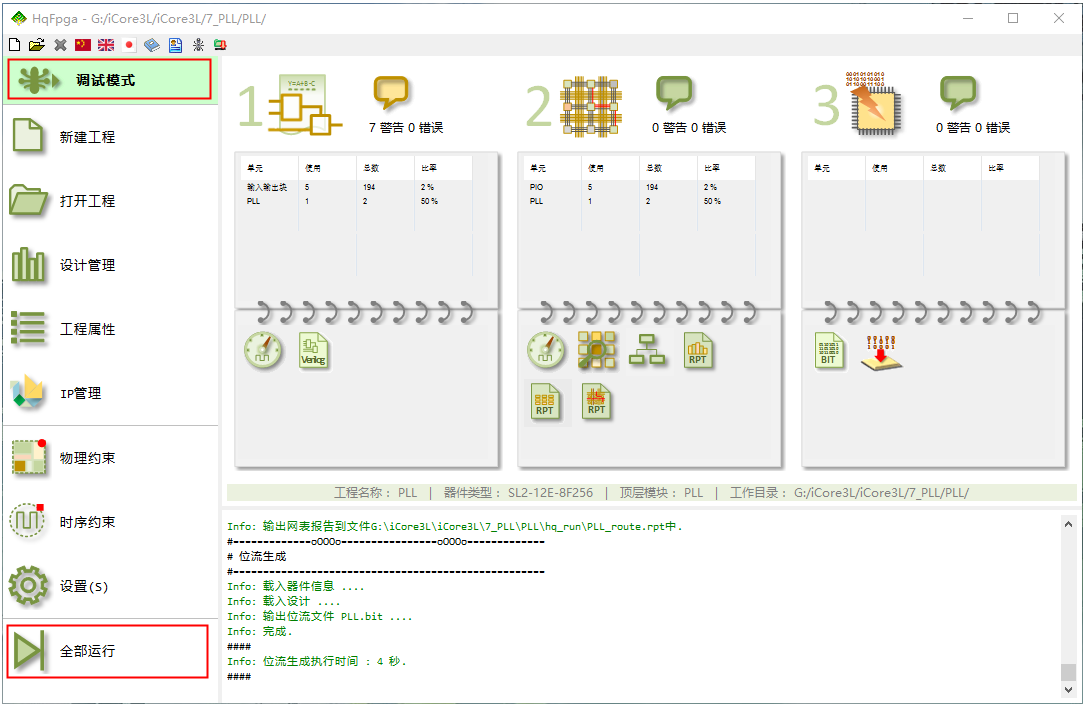

1、首先点击左侧边栏的“全部运行”按钮,生成位流文件;然后点击左侧边栏的“调试模式”按钮,进入调试模式。

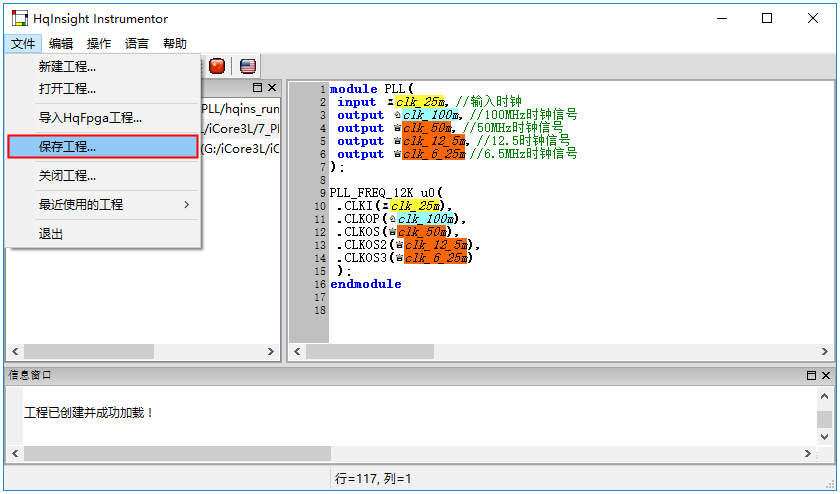

2、调试界面点击“采集调试信息”按钮,弹出窗口中,首先将100MHz信号设置为采样时钟信号,其余的输出时钟信号设置为仅采样,输入信号设置为仅触发;然后点击“配置IICE”,将采样时钟配置为100MHz,采样深度设置为8192,最后点击“文件”→“保存工程…”,并退出此界面。

3、点击第二项“实现→下载”,将bit文件下载到FPGA。

注意:是Hqins_run文件夹下的bit文件。

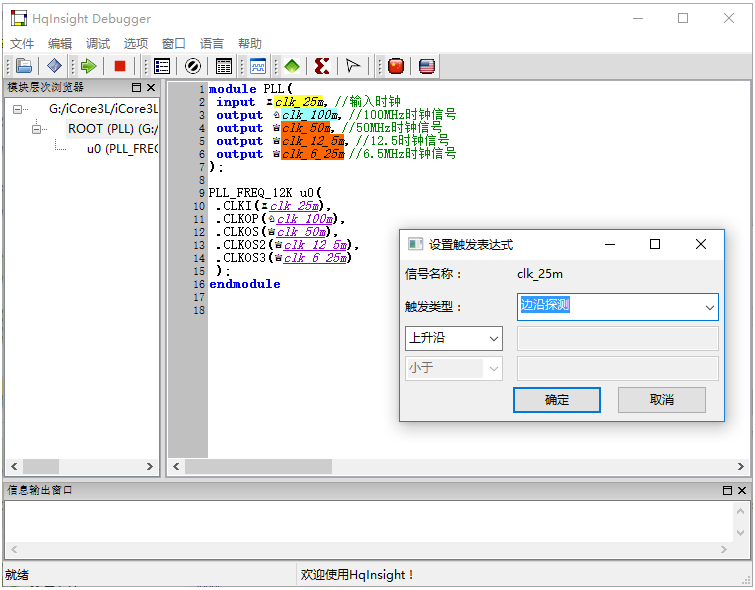

4、点击“实时调试”按钮,弹出窗口中单击clk_25m,设置触发表达式,然后点击确定。

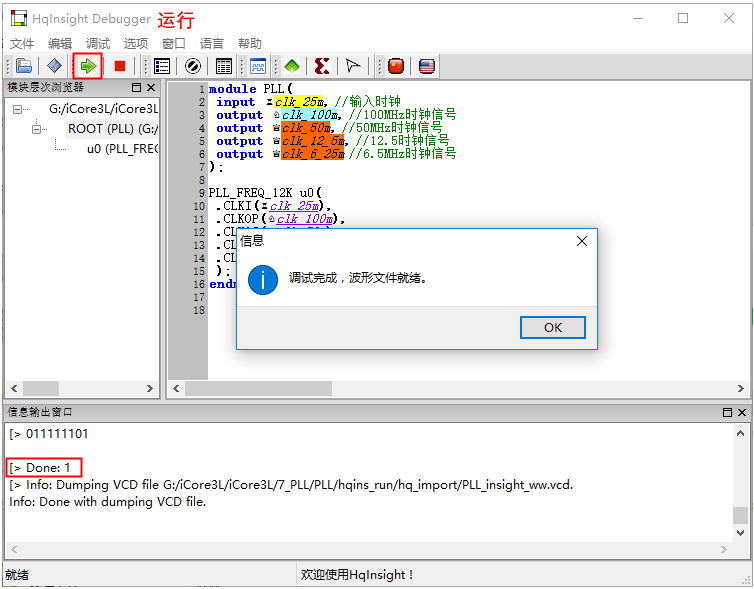

5、然后点击“运行”按钮,运行完毕,弹出“调试完成,波形文件就绪”的提示。

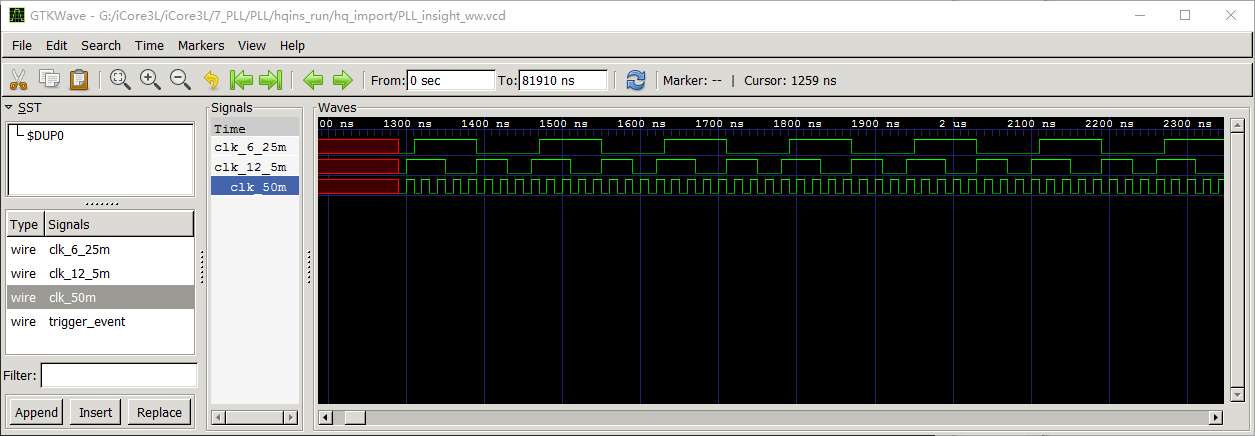

6、点击“波形”按钮,弹出的GTKWave窗口Signals栏添加采样信号,可以看到波形如下图所示,说明PLL IP核模块产生了预期的时钟信号。

五、 代码讲解

- 本实验代码并不多,通过例化的方式对PLL IP核进行了调用,并将PLL IP核的输出信号引到模块的输出端口。代码如下:

module PLL( input fpga_clk, output clk_100m, output clk_50m, output clk_12_5m, output clk_6_25m ); //--------------------PLL IP Core------------------------------// PLL_FREQ_5K_25K u0( //例化PLL 模块 .CLKI(fpga_clk), //25MHz系统时钟输入 .CLKOP(clk_100m), //100MHz输出信号 .CLKOS(clk_50m), //50MHz输出信号 .CLKOS2(clk_12_5m), //12.5Mhz输出信号 .CLKOS3(clk_6_25m) //6.5MHz输出信号 ); //末尾要加分号,模块信号前面的点不能少 //--------------------end module------------------------------// endmodule

- 对IP核例化的语法格式如下:

IP核模块名 例化名( .IP核信号列表 (连接到IP核该端口的信号), .IP核信号列表 (连接到IP核该端口的信号), ... ... .IP 核信号列表 (连接到IP核该端口的信号) );

- 上面语法格式中,IP核模块名也可以是用户写的其他模块的名字,即例化其他模块;例化名则可以由用户定义,可以和模块名相同,也可以不同。当调用其他模块时,例化名前面是被调用模块的名字。点后面的信号列表为被调用模块的端口信号,而其后括号中的信号列表则是连接到被调用模块端口的变量。

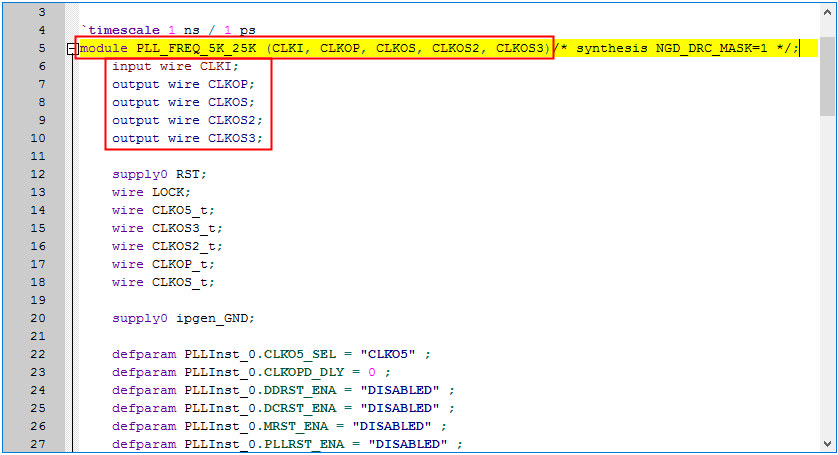

- 双击左侧栏的PLL IP核源文件(u0:PLL_FREQ_5K_25K),可以看到如下图中所示内容;黄色字体行,包含了PLL IP核的模块名和端口列表;通过在顶层模块内调用PLL IP核模块,以模块例化的方式将PLL的输出信号连接到顶层模块。

六、 拓展实验

1、更改输出信号的相位和占空比参数,观察HqInsight采样结果有何不同。