| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2019-02-19 | gingko | 初次建立 |

实验五:Signal Tapll 实验——逻辑分析仪

一、 实验目的与意义

- 了解 Signal TapII 逻辑分析仪

- 掌握 Signal TapII 逻辑分析仪方法

- 掌握 QuartusII 集成开发环境使用方法

二、 实验设备及平台

三、 实验步骤

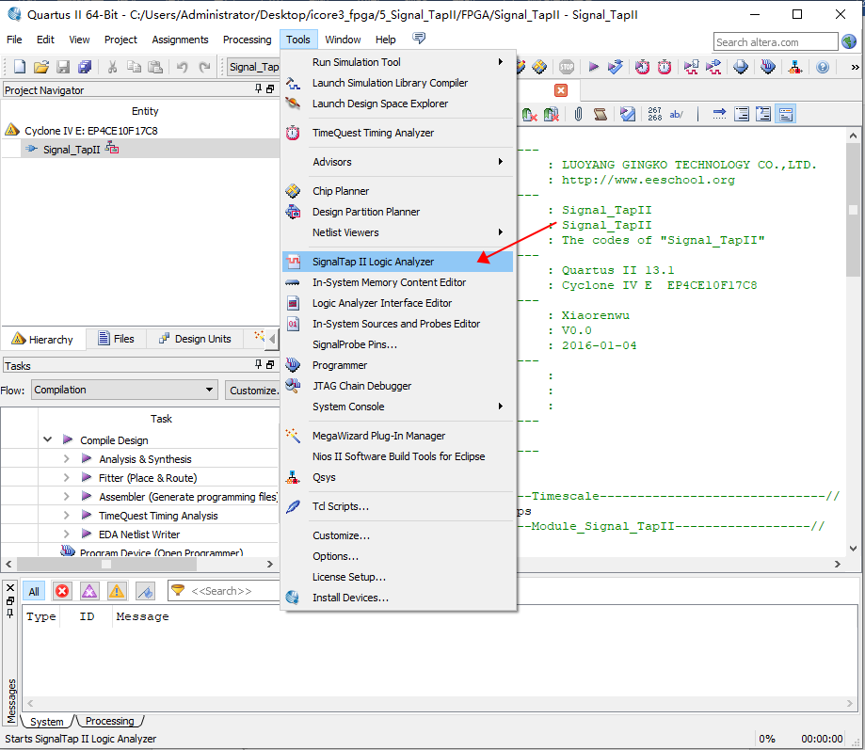

1、 首先确保你的工程已经完成(包括引脚配置,I/O 设置等),然后编译工程。连接开发板 与 Blaster 仿真器,对开发板上电,完成之后打开 tool –> signaltapII logic analyzer.

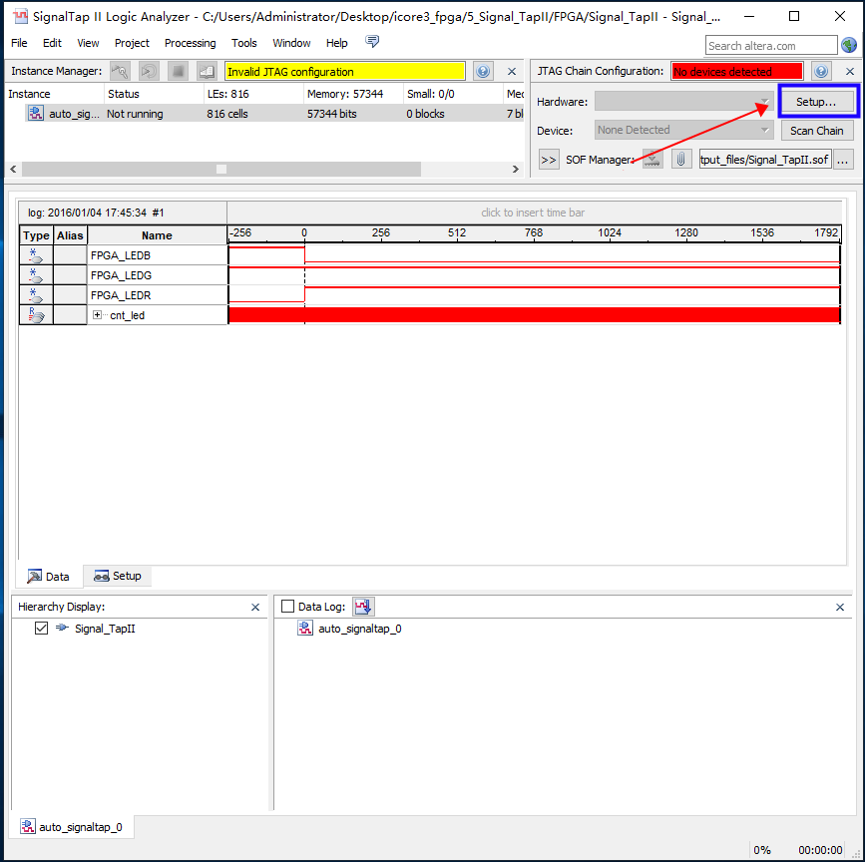

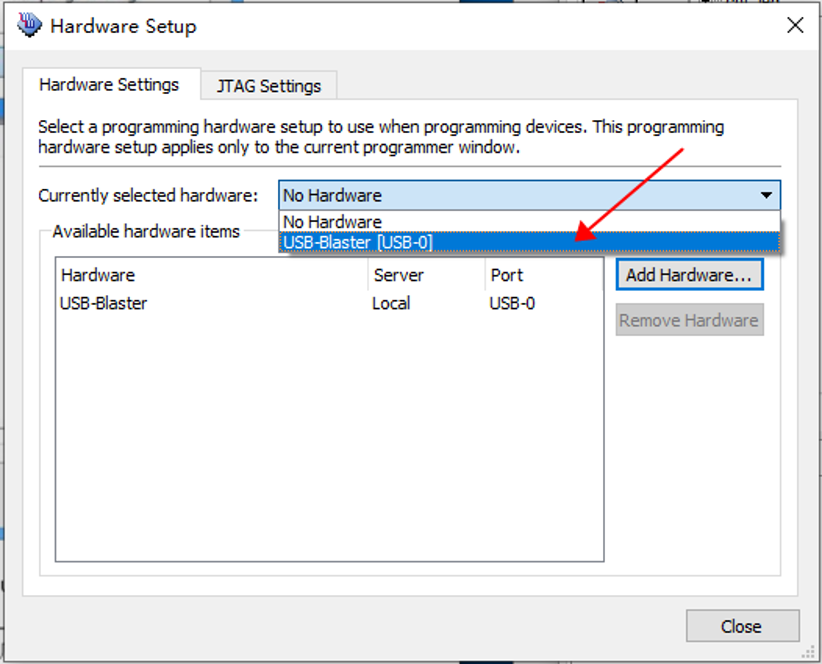

2、 点击方框处的 setup,在弹出的窗口中选择USB-Blaster[USB-0]选项,点击 close 即可。

2、 点击方框处的 setup,在弹出的窗口中选择USB-Blaster[USB-0]选项,点击 close 即可。

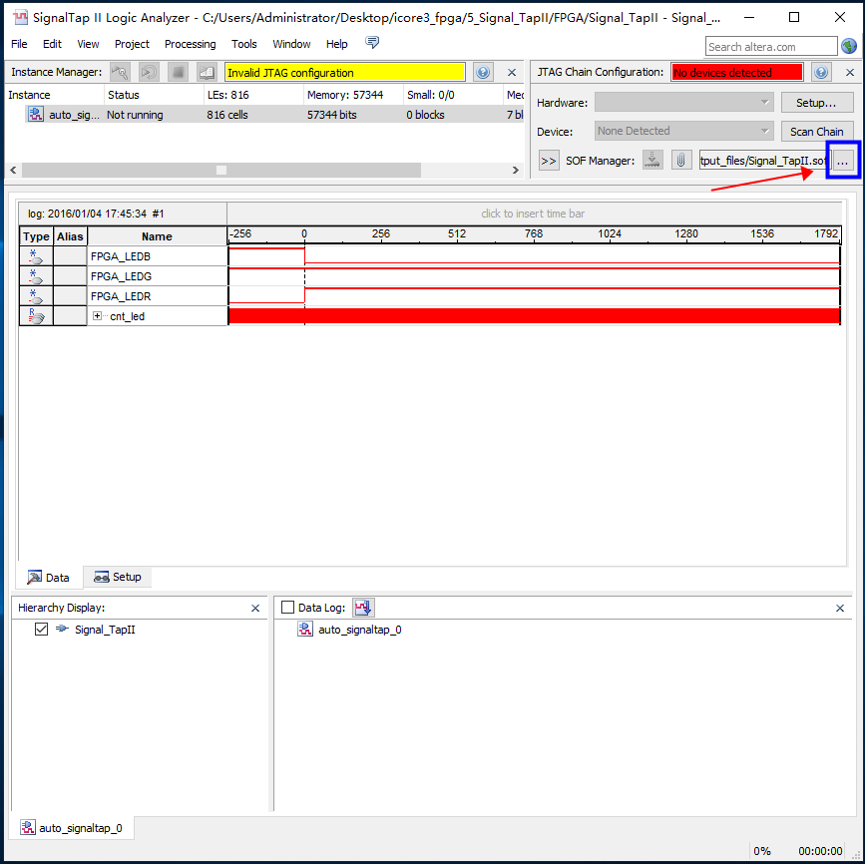

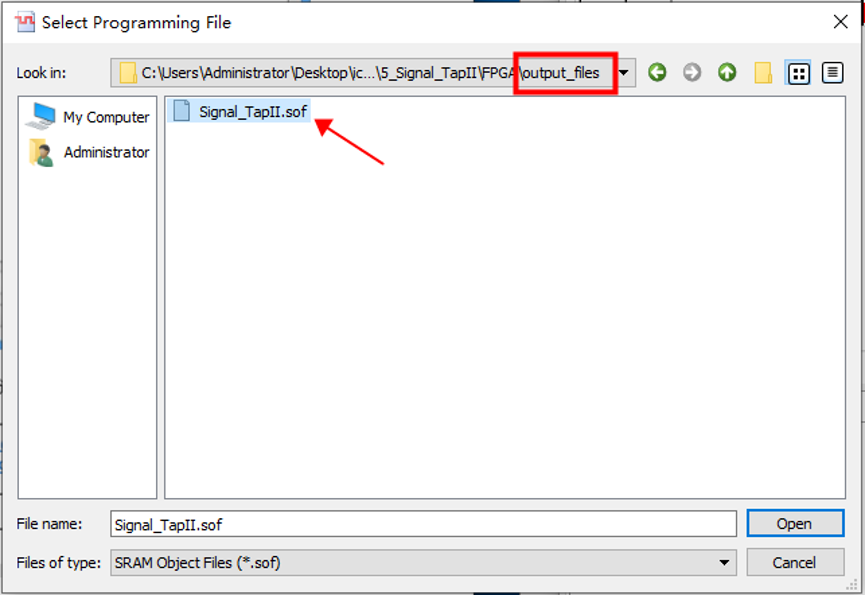

3、 点击方框处添加 sof 文件,一般 sof 文件在工程路径下 output file 文件夹下,点击打开即可。

3、 点击方框处添加 sof 文件,一般 sof 文件在工程路径下 output file 文件夹下,点击打开即可。

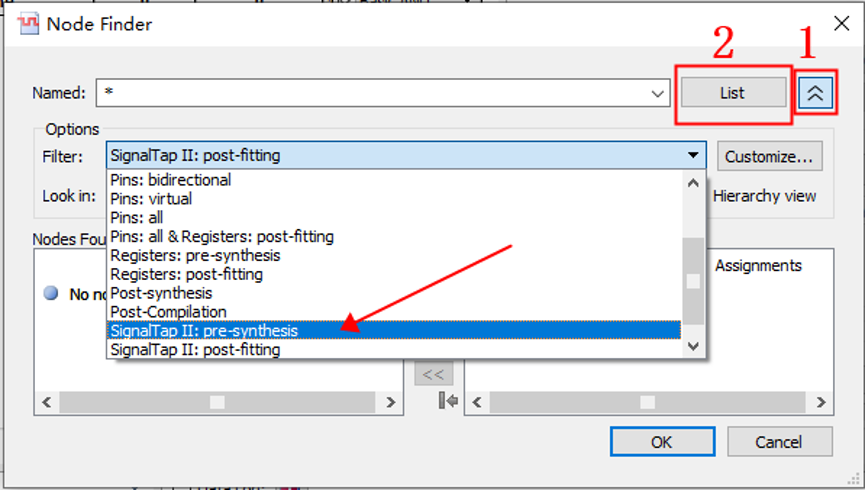

4、 接下来先点击方框 1 处的 setup,再点击方框 2 处进行采样时钟设置,在弹出的窗口中,选择箭头所指的选项,再确定左侧小方框中的图标跟图示相同,然后点击“list”。

4、 接下来先点击方框 1 处的 setup,再点击方框 2 处进行采样时钟设置,在弹出的窗口中,选择箭头所指的选项,再确定左侧小方框中的图标跟图示相同,然后点击“list”。

5、 选中左侧信号列表里的时钟信号,点击中间方框中的按钮,该信号会加入到右边栏里,点击 OK

5、 选中左侧信号列表里的时钟信号,点击中间方框中的按钮,该信号会加入到右边栏里,点击 OK

6、 接下来设置采样深度,这里选择2k。采样深度受FPGA逻辑资源的限制,也就是采样占用的FPGA逻辑资源和逻辑功能占用的FPGA逻辑资源是有上限的,逻辑功能占用的资源越多,则逻辑分析仪采样所能占用的资源就越少。

6、 接下来设置采样深度,这里选择2k。采样深度受FPGA逻辑资源的限制,也就是采样占用的FPGA逻辑资源和逻辑功能占用的FPGA逻辑资源是有上限的,逻辑功能占用的资源越多,则逻辑分析仪采样所能占用的资源就越少。

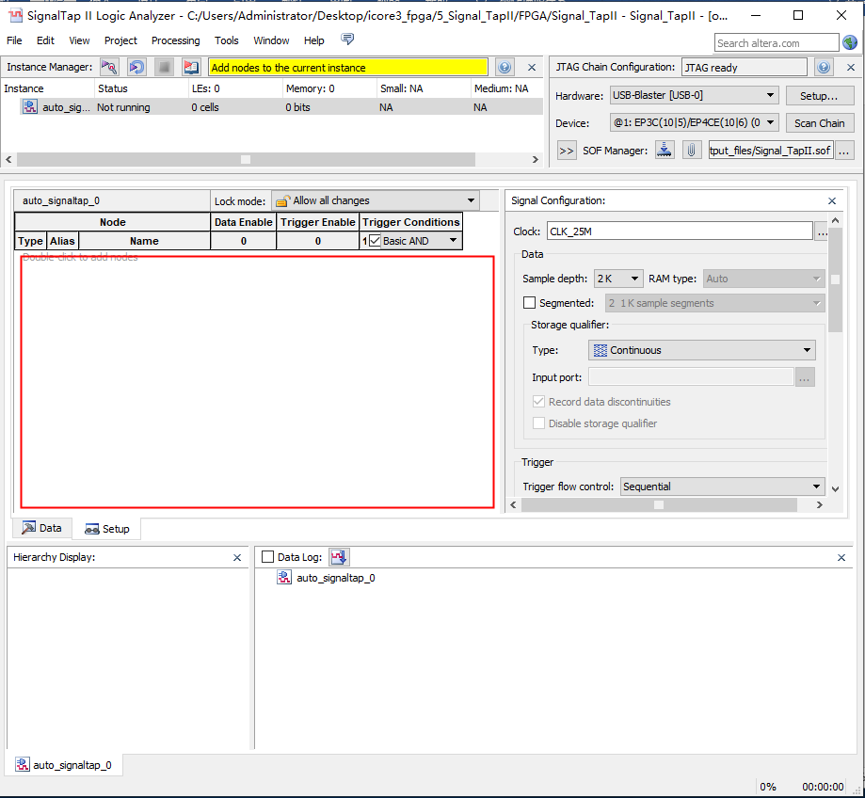

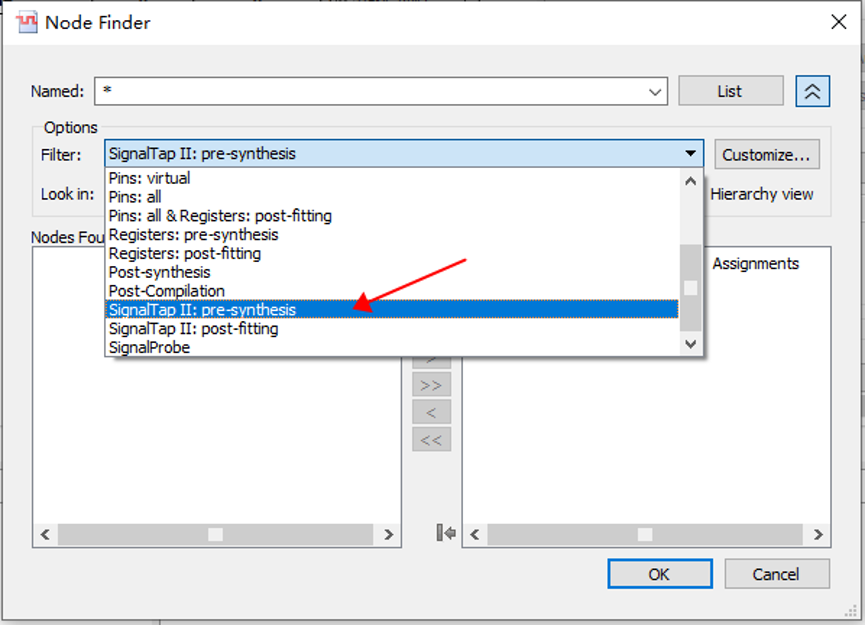

7、 双击左侧方框处的空白来添加要观察的信号,在弹出的窗口中选择箭头处的选项,之后 点击 list。

7、 双击左侧方框处的空白来添加要观察的信号,在弹出的窗口中选择箭头处的选项,之后 点击 list。

8、 选中左侧信号列表里需要观察的信号,点击中间方框中的按钮,信号会加入到左侧栏,也可点击下方反方向的按钮删除信号,点击 OK

8、 选中左侧信号列表里需要观察的信号,点击中间方框中的按钮,信号会加入到左侧栏,也可点击下方反方向的按钮删除信号,点击 OK

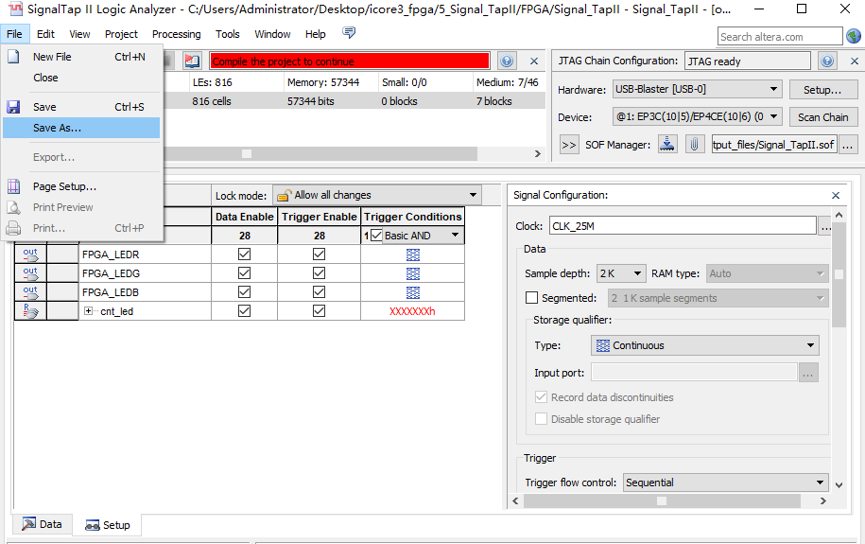

9、 保存该分析文件,点击 file → save as ,填写文件名称,点击保存即可。

9、 保存该分析文件,点击 file → save as ,填写文件名称,点击保存即可。

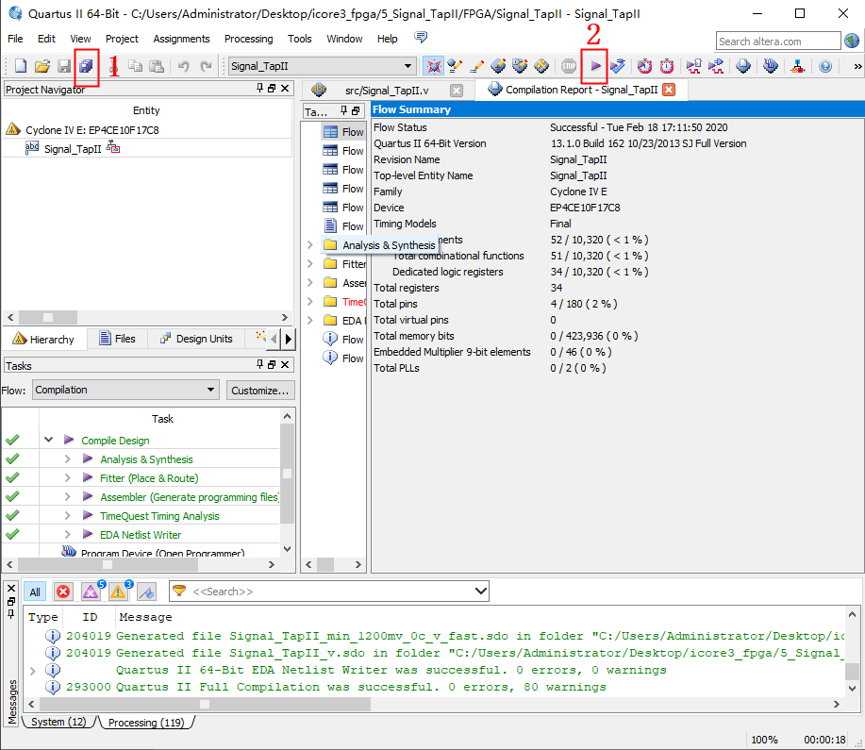

10、 回到主窗口点击全部保存,并编译,如图示。

10、 回到主窗口点击全部保存,并编译,如图示。

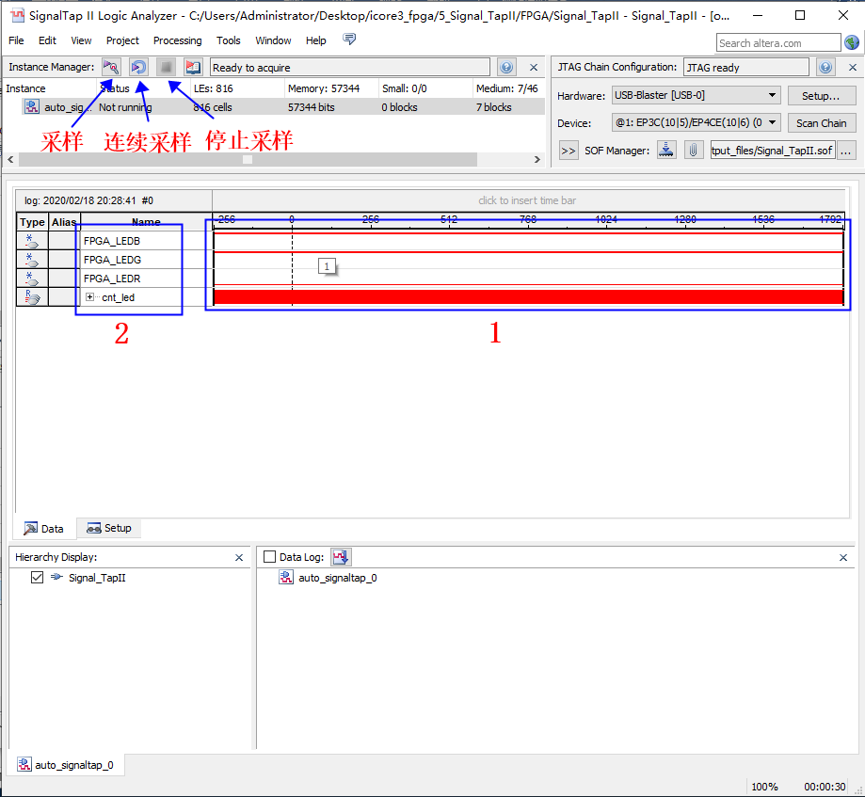

11、 编译完成之后,点击图示 1 处的下载,下载完成之后再点击图示 2 处开始采集。

11、 编译完成之后,点击图示 1 处的下载,下载完成之后再点击图示 2 处开始采集。

12、 此时会看到采集到的波形,图示 1 处是波形窗口,图示 2 处是信号名称

12、 此时会看到采集到的波形,图示 1 处是波形窗口,图示 2 处是信号名称

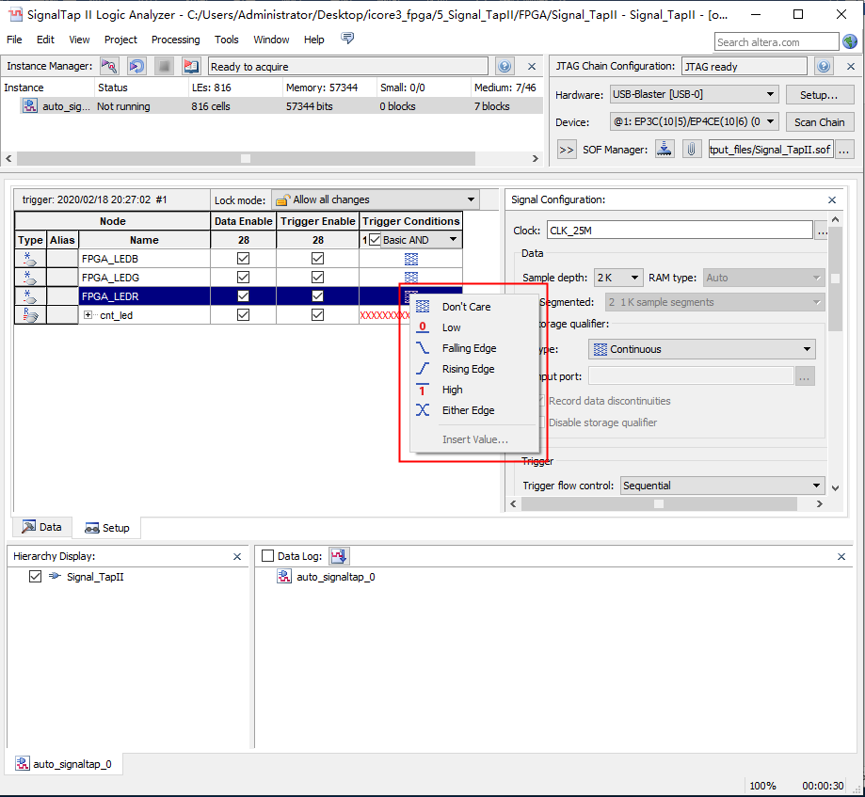

13、 点击方框中的 setup ,选中要设置的信号,鼠标右键单击,可以进行触发方式设置,即检测到设置的触发电平或者触发沿,data界面的信号波形图会显示出符合设置的信号变化。设置好之后重新采集。

13、 点击方框中的 setup ,选中要设置的信号,鼠标右键单击,可以进行触发方式设置,即检测到设置的触发电平或者触发沿,data界面的信号波形图会显示出符合设置的信号变化。设置好之后重新采集。

14、 重新采集,可以看到触发点,如图箭头处,把鼠标放在波形上,左键放大波形,右键缩小波形。

15、 如果已经有逻辑分析文件,可以在主页面上打开 assignment → setting,在左侧栏中选 中 sgnaltapII logic analyzer,在左侧方框处勾选,使能逻辑分析仪即可。打开 tool –> signaltapII logic analyzer.就可使用逻辑分析仪。

15、 如果已经有逻辑分析文件,可以在主页面上打开 assignment → setting,在左侧栏中选 中 sgnaltapII logic analyzer,在左侧方框处勾选,使能逻辑分析仪即可。打开 tool –> signaltapII logic analyzer.就可使用逻辑分析仪。

四、 实验现象

iCore3 双核心板上与 FPGA 相连的三色 LED(PCB 上标示为 FPGA·LED),红色、绿色、 蓝色交替点亮