icore4tx_fpga_5

这是本文档旧的修订版!

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 技术论坛 | http://www.eeschool.org | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-05-09 | gingko | 初次建立 |

实验五:逻辑门实验——基本运算符

一、实验目的与意义

- 学习运算符的定义。

- 掌握Verilog HDL语言中基本运算符的使用方法。

- 掌握QuartusII的使用方法。

二、实验设备及平台

- iCore4TX 双核心板。点击购买

- USB-CABLE(或相同功能)仿真器。

- Micro USB线缆。

- ISE开发平台。

- 电脑一台。

三、实验原理

- 运算符是用来执行程序代码运算的,是一段代码的重要组成部分。在Verilog HDL中按照功能划分,运算符可分为算术运算符、逻辑运算符、关系运算符、条件运算符、按位运算符、拼接运算符、移位运算符、等式运算符、赋值运算符等类型。按照运算符所带的操作数的个数划分可分为3类,即:

- 单目操作符,运算符可带一个操作数;

- 双目操作符,运算符可带两个操作数;

- 三目操作符,运算符可带三个操作数。

- 1、算术运算符

- 在Verilog HDL中的算术运算符有多种,其中最常用的有4种,如表5-1所示。

| 操作符 |执行的操作|操作数个数|表达式|

| + | 加法运算 | 2 | rega + 10 |

| - | 减法运算 | 2 | rega - 10 |

| * | 乘法运算 | 2 | rega * 10 |

| / | 除法运算 | 2 | 23 / 10,运行结果为2 |

* 1、逻辑运算符

- 在Verilog HDL中有三种逻辑运算符,如表5-2所示。逻辑运算的结果只有两种:0(假)和1(真),其逻辑真值如表5-3所示。

| 操作符 |执行的操作|操作数个数|表达式|

| ! | 逻辑求反 | 1 | !a | ||||

| && | 逻辑与 | 2 | a && b | ||||

| 逻辑或 | 2 | a | b | ||||

| a | b | !a | !b | a && b | a | b | |

| 1 | 1 | 0 | 0 | 1 | 1 | ||

| 1 | 0 | 0 | 1 | 0 | 1 | ||

| 0 | 1 | 1 | 0 | 0 | 1 | ||

| 0 | 0 | 1 | 0 | 0 | 0 | ||

四、引脚分配

1、 手动分配引脚

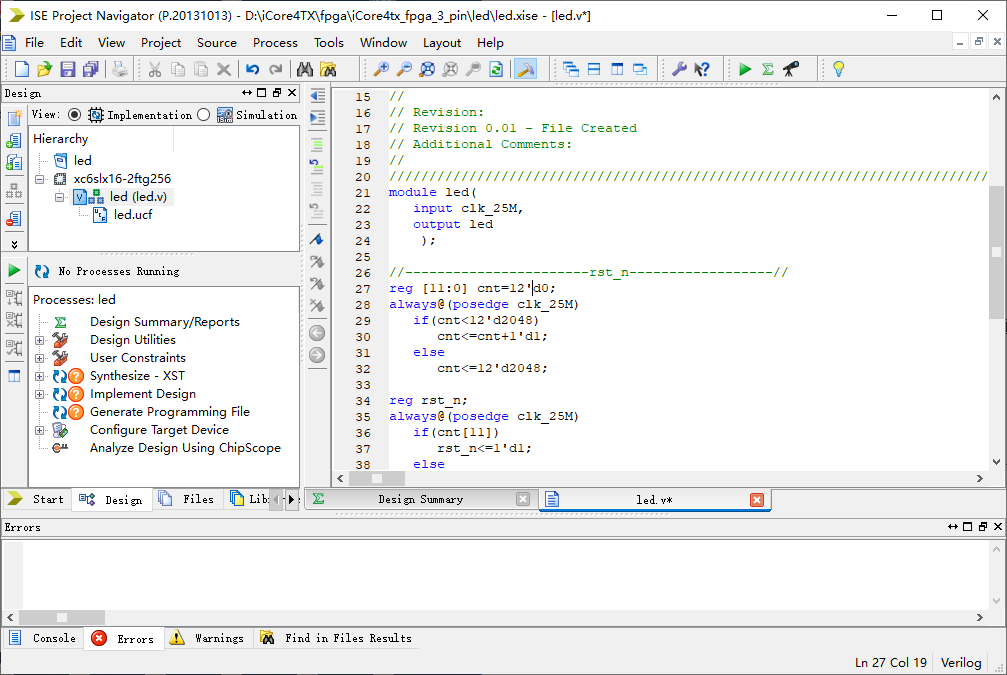

- 1、以实验二led工程为例,打开工程,如图3.1所示。

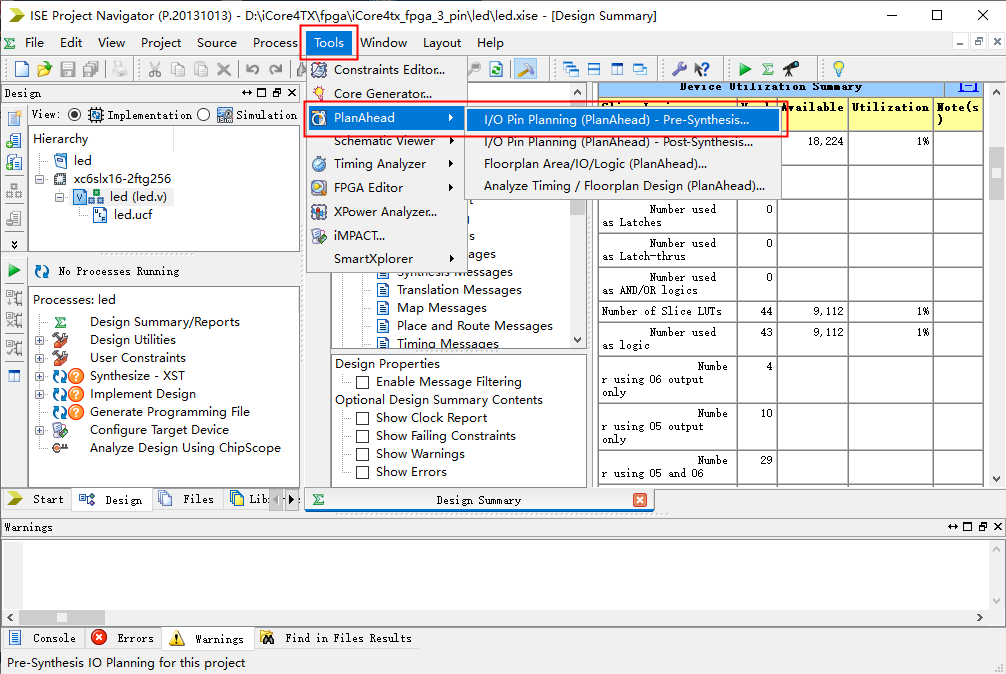

- 2、点击工具栏Tools,下拉才当中选中PlanAhead I/O Pin Planning(PlanAhead) – Pre – Synthesis…。

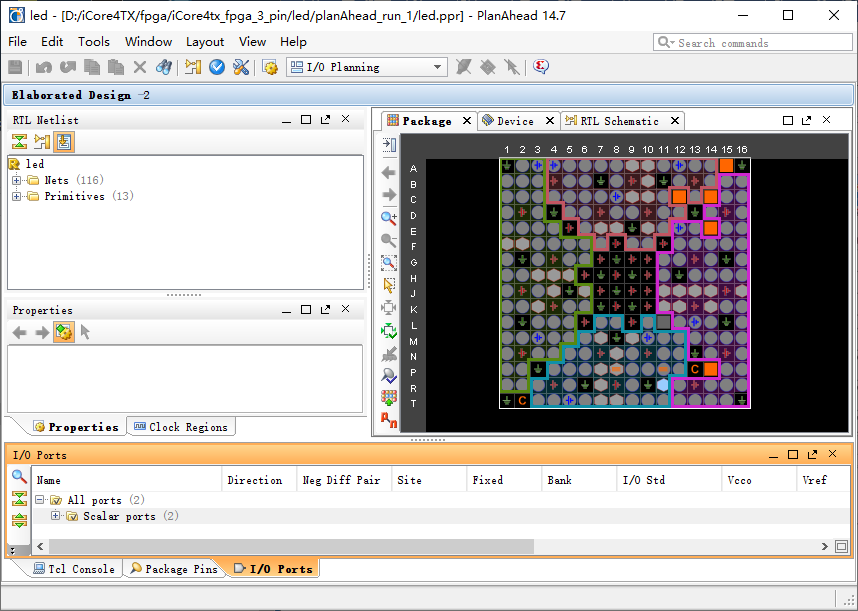

- 3、如果有提示点击Yes,稍等片刻后可能会弹出欢迎界面,关闭欢迎界面,然后视图如下:

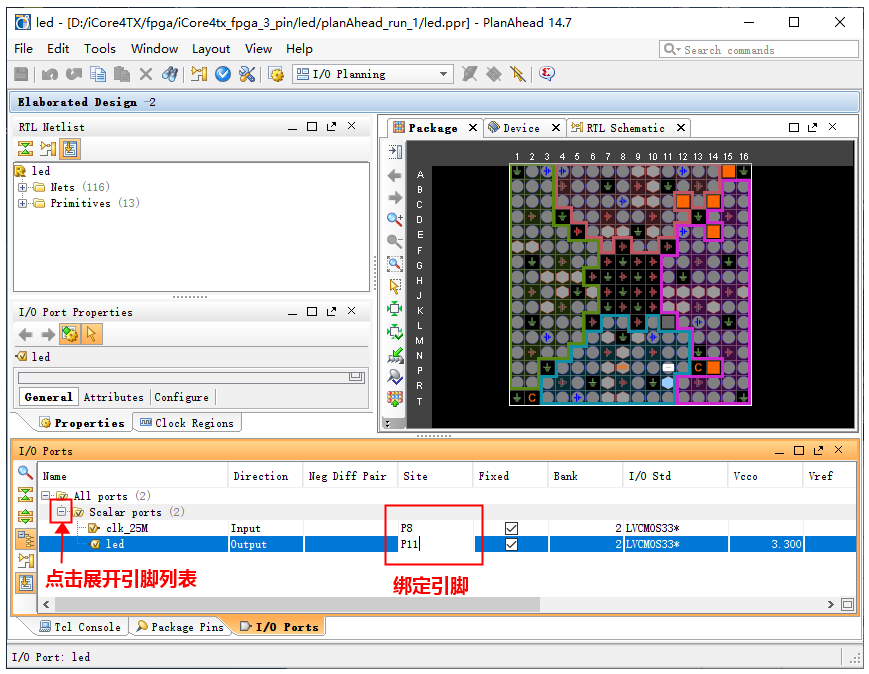

- 4、在I/O Ports栏下面,点击Scalar ports 前面的“+”,展开引脚列表;然后在对应引脚的Site栏选定引脚标号,完成引脚的绑定。如下图所示。

- 5、分配好以后关闭该对话框,重新进行编译;如果编译无报错,则引脚分配完成。

2、TCL文件分配引脚

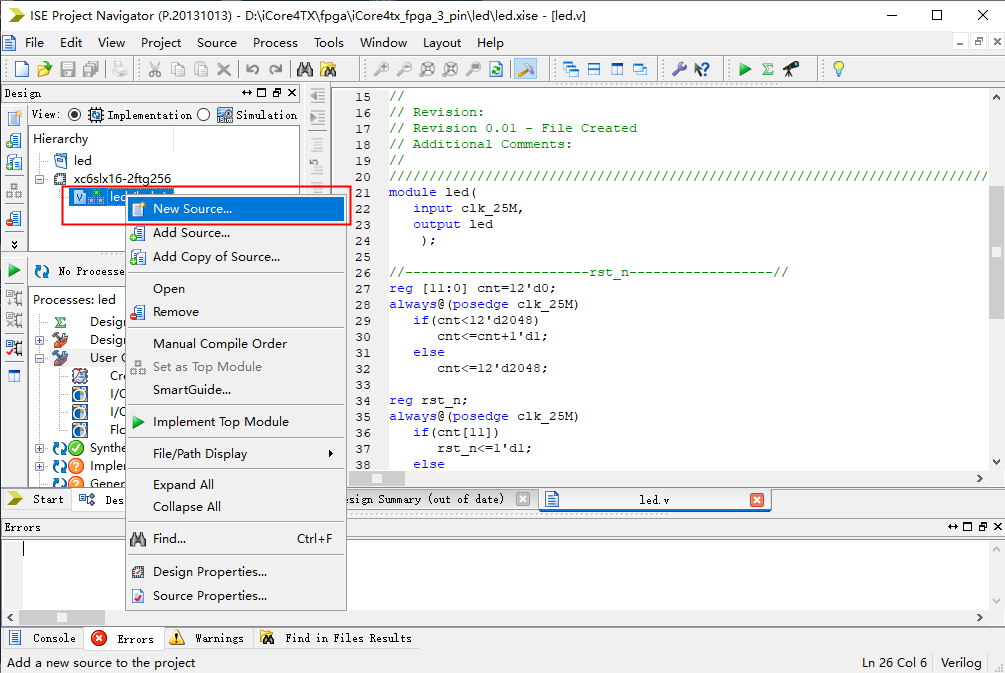

- 1、还是以实验二LED实验为例,选中工程,右键点击New Source …。

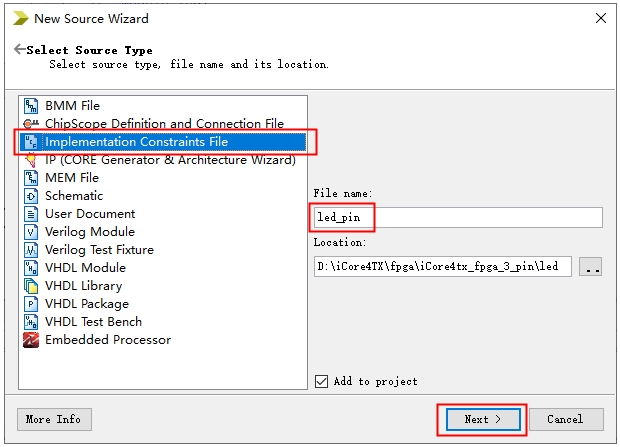

- 2、新建文件类型为Implementation Constraints File,File name栏输入文件名,如下图所示,然后点击Next。

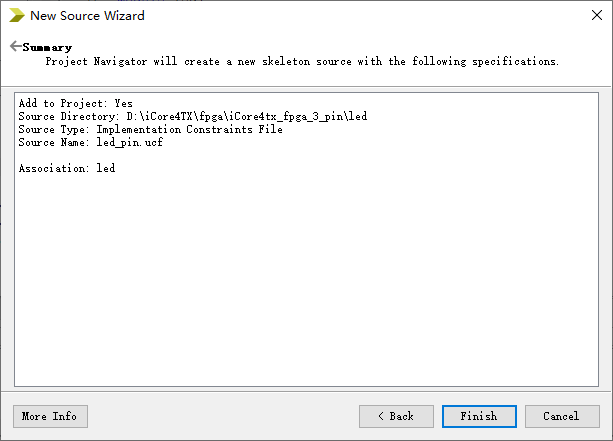

- 3、点击Finish。

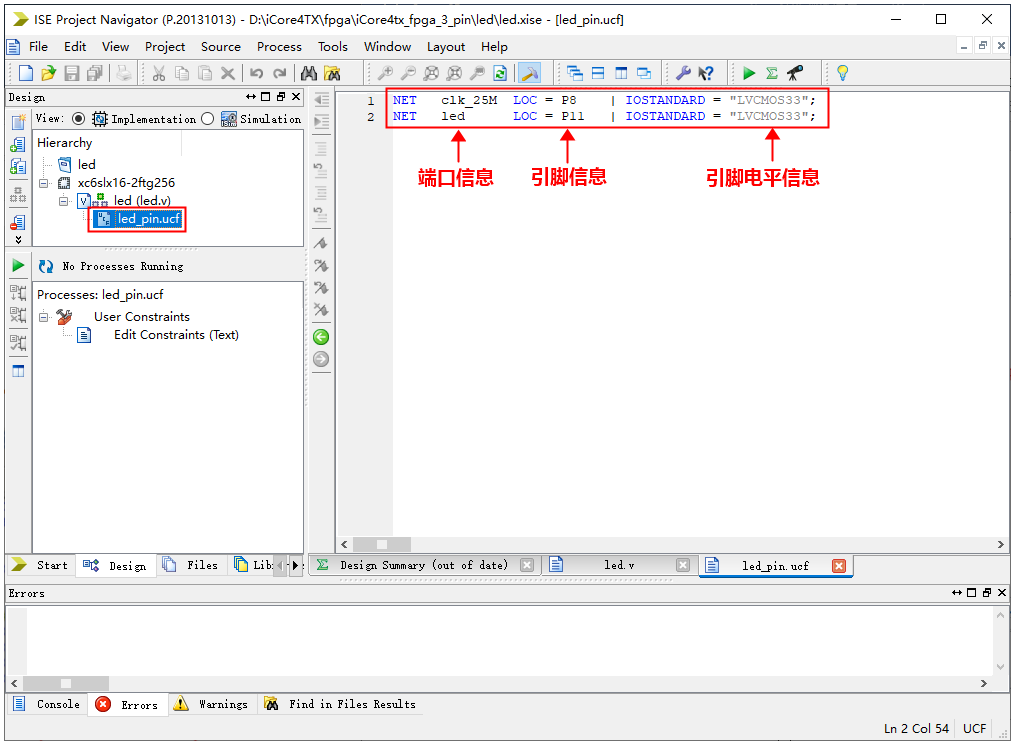

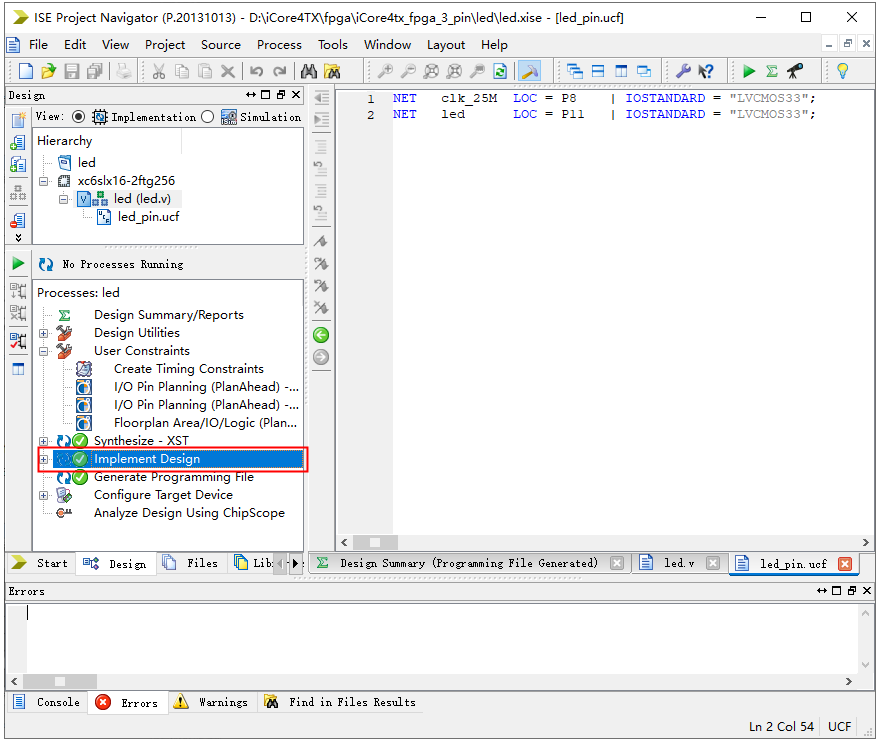

- 4、可以在左侧边栏看到工程目录下多了一个.ucf格式的文件,在右边编辑区输入下图中的引脚约束信息,如图所示;引脚约束信息的语法定义如下:

- NET “端口名称” LOC = 引脚编号 | IOSTANDARD = “电压”

- 5、点击保存,并编译工程;如果信息输入正确,编译通过,则Implement Design 前面会出现绿色“√”;则引脚分配完成。

五、实验步骤

- 将iCore4TX连接下载器和USB供电线;

- 分别按照手动分配引脚方式和.ucf文件分配引脚方式分配引脚并编译整个工程。

- 分别将编译后的工程下载至iCore4TX,并观察现象。

六、实验结果

- 可以观察到iCore4TX 的FPGA_LED 闪烁。

icore4tx_fpga_5.1588988992.txt.gz · 最后更改: 2020/05/09 09:49 由 fmj