icore3lfpga_2

这是本文档旧的修订版!

| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 技术论坛 | http://www.eeschool.org | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-10-13 | zgf | 初次建立 |

实验二:新建FPGA工程——驱动LED

一、 实验目的与意义

- 学习HqFpga软件新建工程的方法和步骤。

- 学习Verilog语言描述功能模块的基本语法。

二、 实验原理

- 本实验的主要目的是通过点亮三色LED灯,学习HqFpga软件建立工程的步骤流程以及使用Verilog建模语言实现硬件驱动的方法

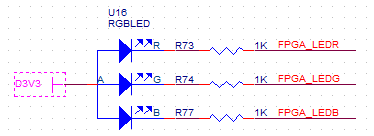

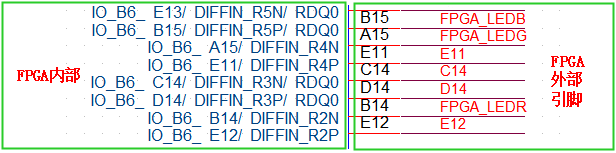

- LED的驱动原理是通过程序控制FPGA数字IO的电平变化,实现LED两端电压的压差变化,从而控制LED的亮灭状态切换。其硬件原理图如图2-1所示。

- 从原理图中可以看出,三色LED正极接3.3V,负极分别连接到FPGA的三个引脚。当与三色LED相连的FPGA某一个引脚为低电平,对应颜色的发光二极管两端正负极压降为3.3V,则LED就会点亮。根据此原理,只需控制和发光二极管相连的FPGA引脚的电平变化,即可实现三色LED色彩和亮灭控制。

三、 建立工程

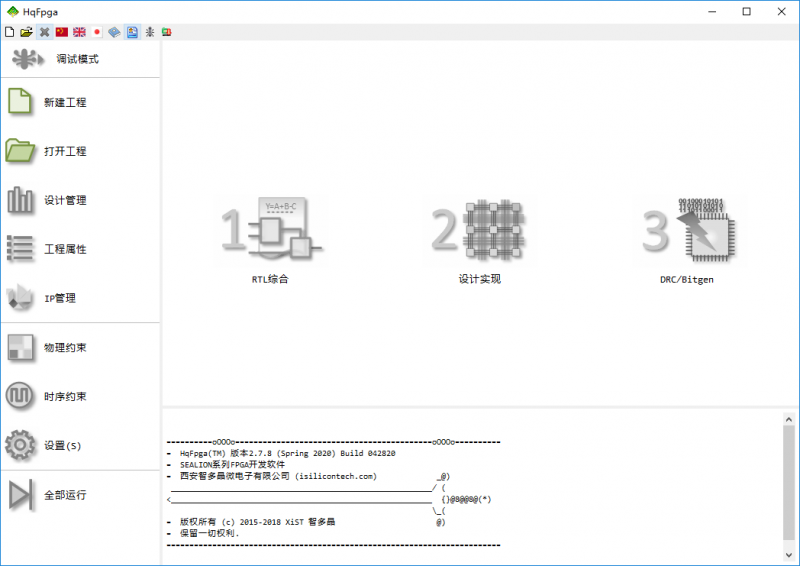

- 1、通过双击安装目录/hqui/子目录下的可执行文件hqui.exe启动HqFpga GUI,可以看到HqFpga界面包含三个主操作按钮:RTL综合、设计实现、DRC\Bitgen,如图2-2所示。

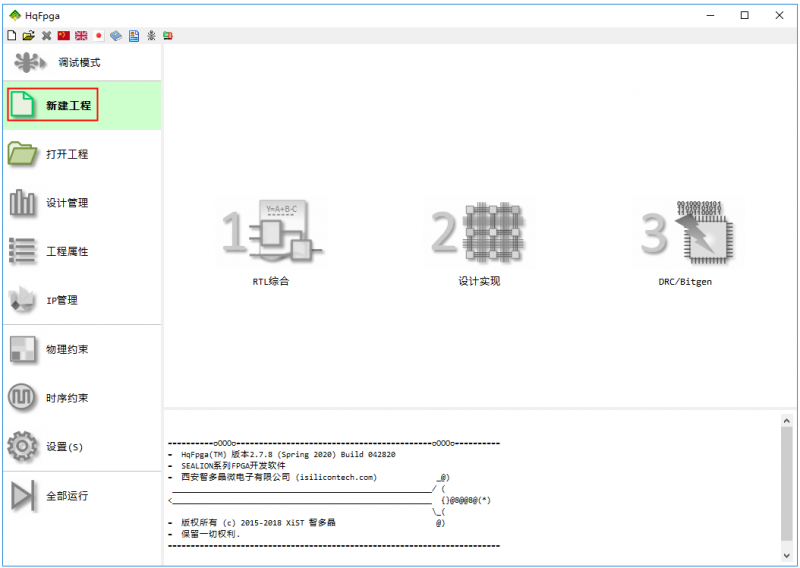

- 2、点击左侧栏中的“新建工程”按钮,建立新工程。

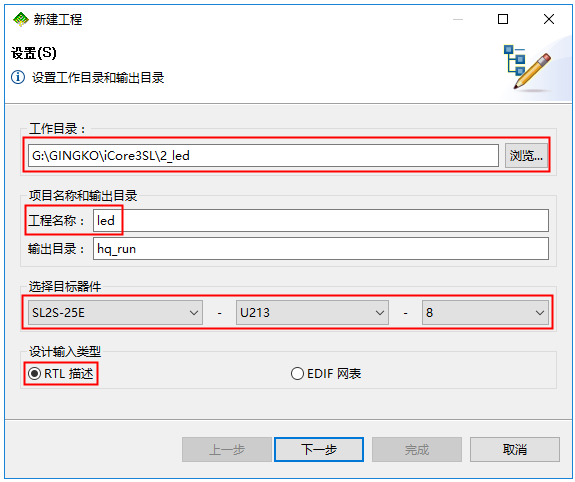

- 3、弹出新建工程向导对话框,在“工程目录”栏设置工程存放路径;在“工程名称”栏填写工程名称,这里以“led”为例; iCore3L双核心板的FPGA采用国产器件,西安智目标器件选择SL2S-25E,设计输入选择RTL描述;然后点击“下一步”。

- 注意:

- 不能把工作目录放在Windows的系统目录及其子目录下,包括(但不限于):桌面目录:C:\user\…\desktop, windows目录C:\Windows,程序安装目录C:\Program Files 或 Program Files(X86),等等。另外,工作目录名称中不能包含特殊字符,例如空格、括号等,也不建议包含中文字符。

- 4、弹出的新建工程窗口中,可以通过点击“+”号添加源文件;也可以直接点击完成按钮跳过添加源文件。这里点击“完成”按钮,后面编写源文件。

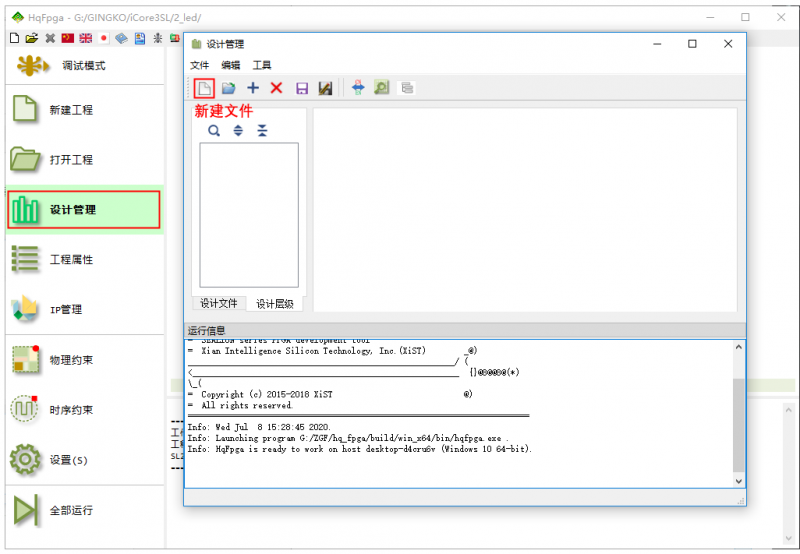

- 5、至此已经建立了工程,然后点击左侧栏的“设计管理”按钮,弹出“设计管理”界面;点击“新建文件”图标,建立源文件,如图2-6所示。

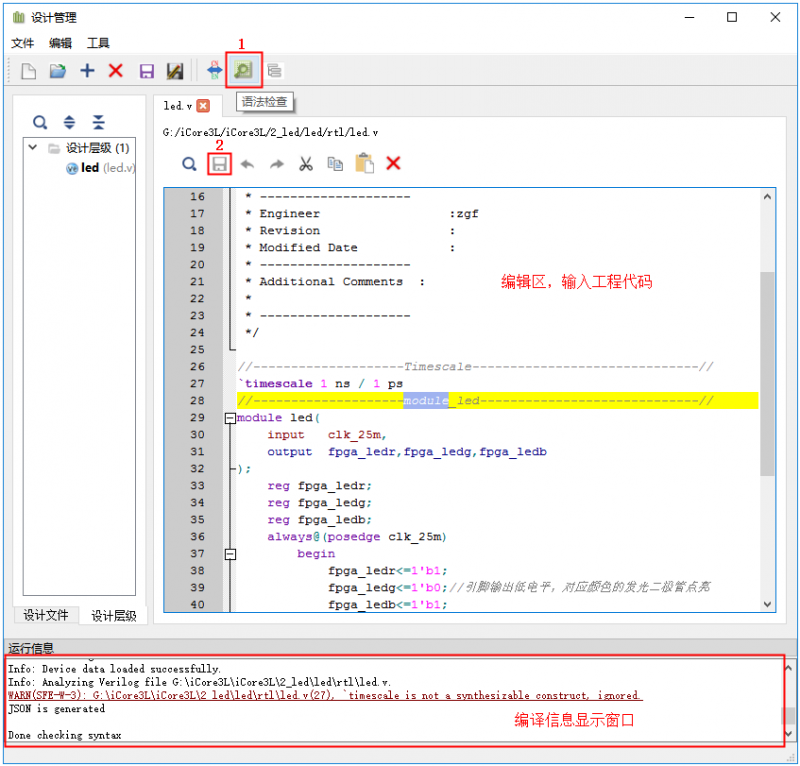

- 6、在设计管理界面的编辑区输入工程代码,点击“语法检查”按钮,检查语法错误;语法检查通过后,点击“保存”按钮图标,并命名为led.v;然后点击3标号处的“+”号,将保存的led.v添加到工程中。

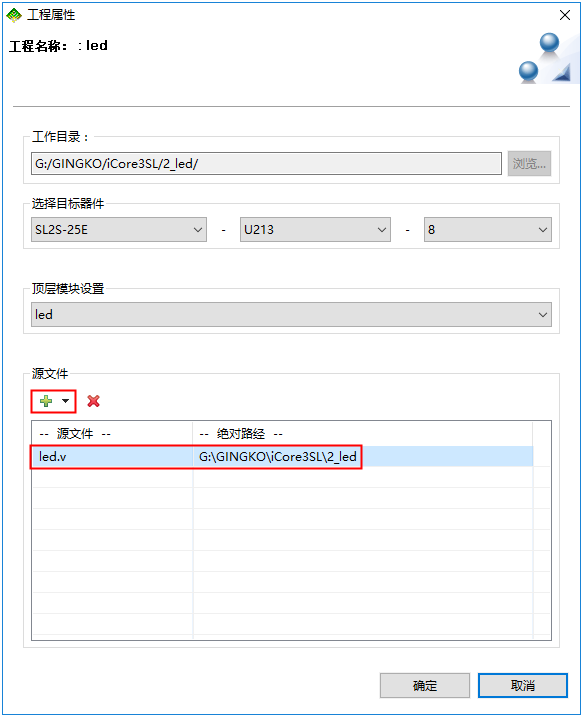

- 7、或者在保存完led.v文件后,关闭“设计管理”界面,再点击左侧边栏的“工程属性”按钮,弹出窗口中点击“+”号,添加刚刚建立的led.v文件,并点击“确定”,如图2-8所示。

- 8、至此,工程建立完成,点击“RTL综合”按钮,运行指定的RTL综合工具。

- 9、综合完成后,可以看到界面上产生一个大的活页标签,如图2-10中所示;标签上半部分显示综合后的FPGA资源利用概要信息。下半页显示有时序分析和网表文件两个标签。

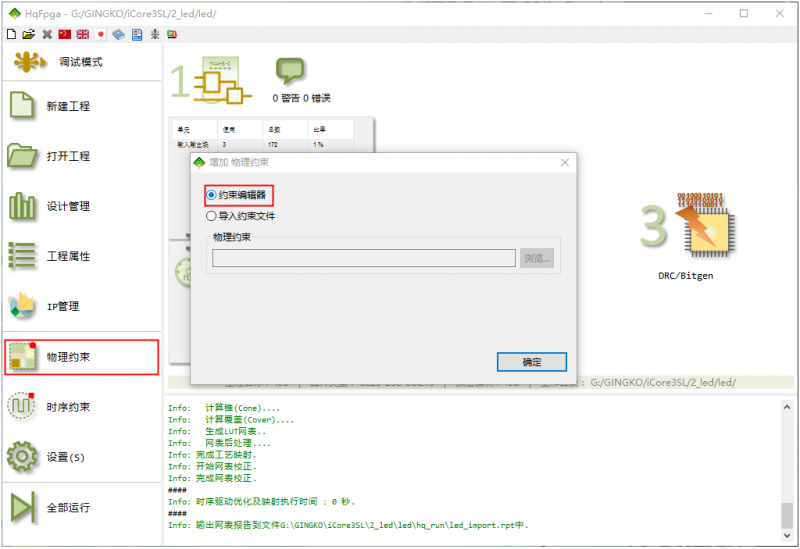

- 10、点击左侧栏“物理约束”按钮,添加约束;弹出窗口点击选中“约束编辑器”,然后点击“确定”。

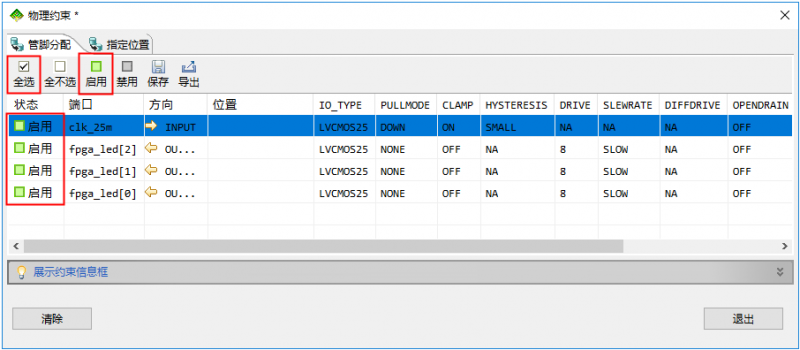

- 11、弹出物理约束窗口,首先点击“全选”,然后点击“启用”,可以看到下方信号列表的状态一栏都变成了启用,如图2-12中所示。

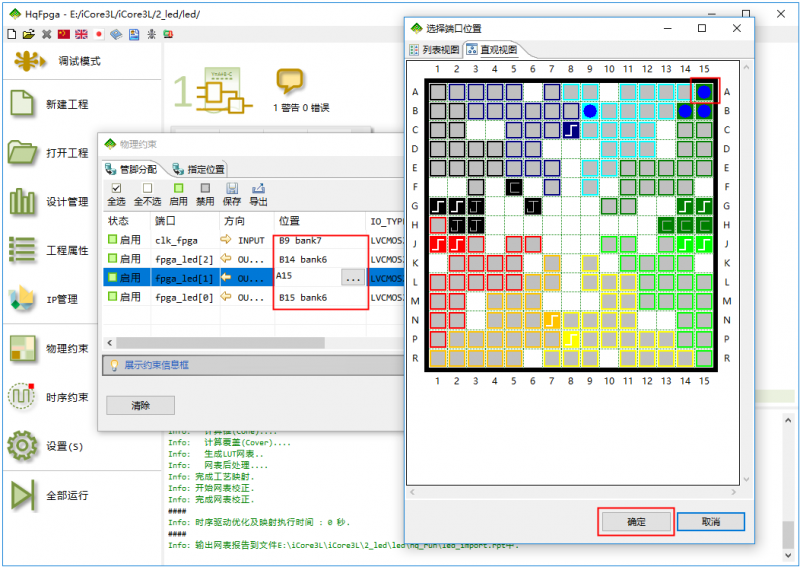

- 12、然后在信号行的“位置”栏下单击,会出现一个带“…”的方框,点击方框,弹出“选择端口位置”窗口,通过单击相应位置,为信号添加引脚约束;之后点击确定,即实现信号对应引脚的绑定。图2-14中以clk_25m为例,绑定到B9引脚,绑定之后,其对应“位置”列出现“B9 bank7”字样。

- 引脚绑定全部完成之后,点击“保存”按钮,然后点击“退出”。

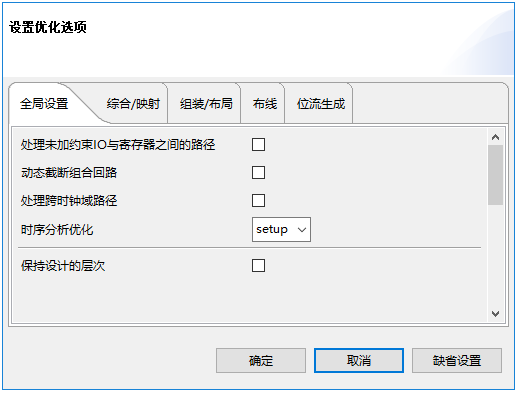

- 13、完成了RTL综合、添加了约束之后,可以在“设计实现”之前对各个步骤设置不同的优化选项;点击界面左侧栏的“设置”按钮,弹出“设置优化选项窗口”,可以进行综合、布局布线等步骤的优化设置。

- 这里选择默认设置,点击“确定”按钮即可。

- 14、点击主界面的“设计实现”按钮;设计实现运行完毕生成一个大的活页标签;标签上半部分是显示FPGA资源使用情况,下半部分是生成的是一些报告和网表文件,可用于分析检查设计实现结果。

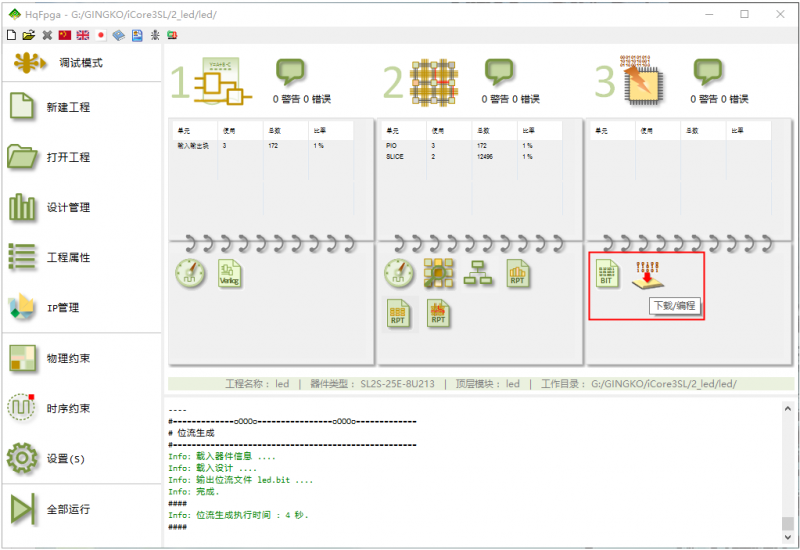

- 15、点击“DRC/Bitgen”按钮,进行设计规则检查(DRC)并生成位流(Bitstream)文件,检查运行结果。

- DRC通过后,在产生活页的下半页有“位流文件”和“下载编程”两个图标。

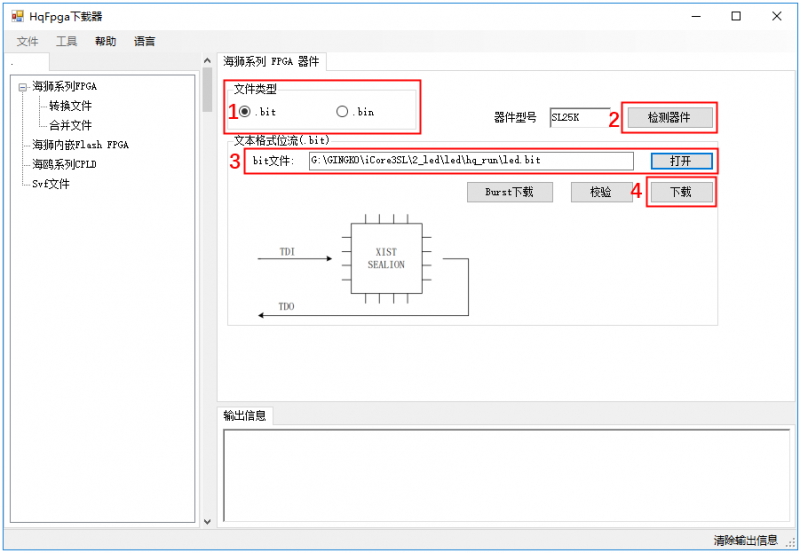

- 16、将下载器和核心板与电脑连接,并给核心版供电。点击DRC活页中的“下载/编程”图标,弹出“HqFpga下载器”界面;此界面下文件类型选择 .bit,点击“检测器件”按钮,查看检测到的器件型号和工程设计中选择的器件型号是否一致;然后点击“打开”按钮,找到生成的led.bit文件并选中,点击“下载”按钮。

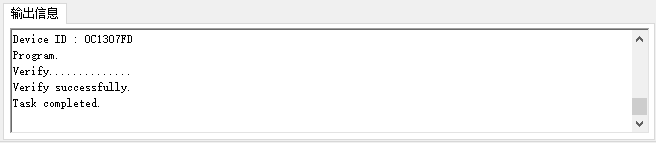

- 17、下载成功将会看到“输出信息”栏有如图2-18所示提示,且开发板上三色LED显示绿色。

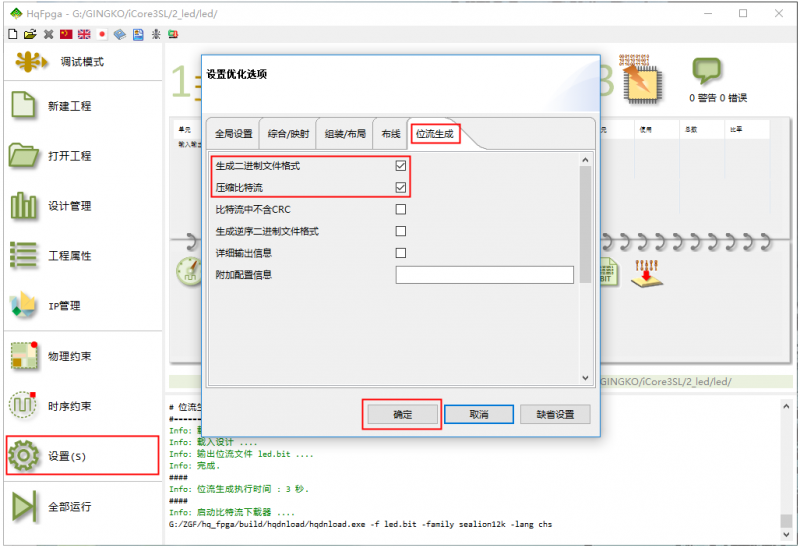

- 18、HqFpga软件默认生成 .bit文件,可用于JTAG模式下载。也可生成 .bin文件,用于mspi模式下载;生成 .bin文件的操作如下:

- 点击左侧栏“设置”按钮,弹出的“设置优化选项”窗口中点击“位流生成”页,勾选“生成二进制文件格式”选项和“压缩比特流”选项,点击“确定”,如图2-19所示。

- 设置好之后重新编译即可生成 .bin文件。

四、 代码分析

- 前面通过对各个步骤的详细介绍,讲述了从建立工程到编译下载实现的整个过程,下面对工程代码做个讲解。

- 本工程较为简单,代码也很简短。首先是关键字module,它和endmodule关键字定义一个模块,关键字module后面的字符就是模块的名字,本工程中模块的名字为led。

- 接着是模块的端口,即位于模块名后面小括号里的变量。本工程led模块有输入时钟和用于控制三色LED的输出,如下面代码中所示。

module led( input clk_fpga,//25MHz output [2:0] fpga_led ); reg fpga_ledr; reg fpga_ledg; reg fpga_ledb; always@(posedge clk_fpga) begin fpga_ledr<=1'b1; fpga_ledg<=1'b0;//引脚输出低电平,对应颜色的发光二极管点亮 fpga_ledb<=1'b1; end assign fpga_led={fpga_ledr,fpga_ledg,fpga_ledb}; //--------------------led module end---------------------// endmodule

- 在模块的内部,定义了三个寄存器变量fpga_ledr、fpga_ledg、fpga_ledb;always块以输入时钟的上升沿作为触发条件,控制三个寄存器变量的值分别为1、0、1。assign语句用于将这三个寄存器变量的值传递到控制三色LED的fpga_led变量,使fpga_led[2]=1,fpga_led[1]=0,fpga_led[0]=1,

- 至此实现了输出变量fpga_led的三位二进制值为101,而fpga_led变量对应的三位寄存器是连接到FPGA引脚,进而连接到三色LED的,那么,fpga_led的对应寄存器的值的变换,将直接影响fpga对应引脚的电平变化。即当fpga_led的值为二进制的101时,和fpga_led[1]寄存器对应引脚输出低电平,那么和此引脚相连的led两端的电压将变成3.3V,从而使LED发亮。

- 同理,当fpga_led变量对应的另外两个寄存器的变量为1时,对应引脚输出为高电平,则与这两根引脚相连的led两端电压为0,led不亮。

icore3lfpga_2.1602553385.txt.gz · 最后更改: 2020/10/13 09:43 由 zgf