| 银杏科技有限公司旗下技术文档发布平台 | |||

| 技术支持电话 | 0379-69926675-801 | ||

| 技术支持邮件 | Gingko@vip.163.com | ||

| 版本 | 日期 | 作者 | 修改内容 |

|---|---|---|---|

| V1.0 | 2020-06-29 | gingko | 初次建立 |

实验六:乘法器实验——乘法器IP核的调用

一、 实验目的与意义

- 了解Xilinx FPGA 乘法器IP核。

- 掌握乘法器IP核的使用方法。

- 掌握ISE集成开发环境使用方法。

二、 实验设备及平台

- iCore4TX 双核心板点击购买。

- USB CABLE (或相同功能)仿真器。

- Micro USB线缆。

- ISE开发平台。

- 电脑一台。

三、 实验原理

- 使用FPGA做一些复杂的算法处理时,可能会用到乘法运算;Xilinx FPGA已经在内部集成了硬件乘法运算资源,通过ISE开发软件在工程中调用FPGA内部的乘法器资源,即可实现乘法运算的处理。FPGA调用IP核的方法,可大大提高开发效率,缩短开发周期。

- 本实验主要讲解如何在设计中实现乘法器IP核的调用,以及在ISE中调用乘法器IP核的步骤。并通过乘法器的运算结果,控制连接到FPGA引脚的LED 的状态,实现红色 LED 闪烁的效果。

四、 实验步骤

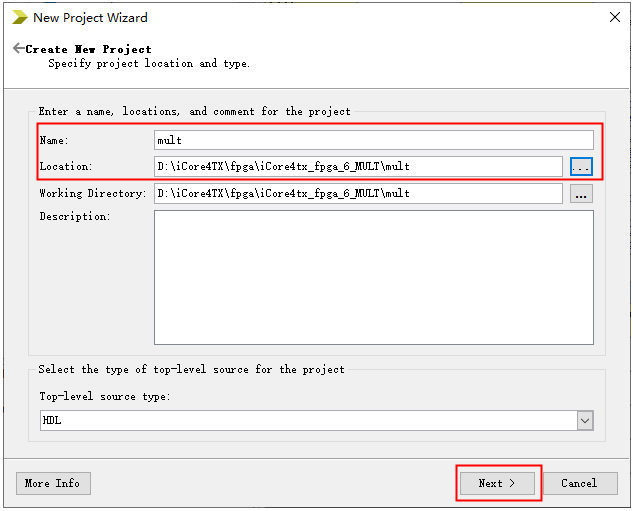

1、双击打开ISE软件,并新建工程,命名为mult,设置好工程存放路径。

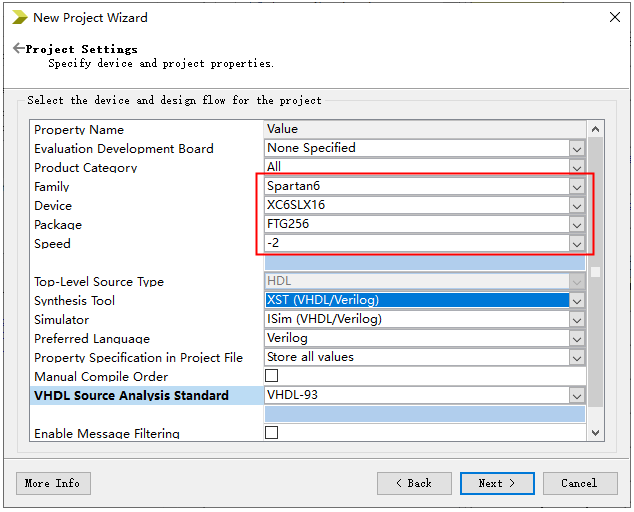

2、选择FPGA器件型号并,点击 Next。

2、选择FPGA器件型号并,点击 Next。

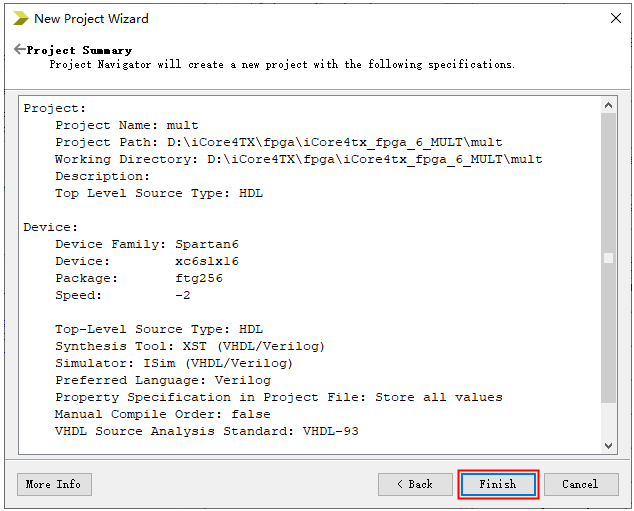

3、点击Finish,建立工程。

3、点击Finish,建立工程。

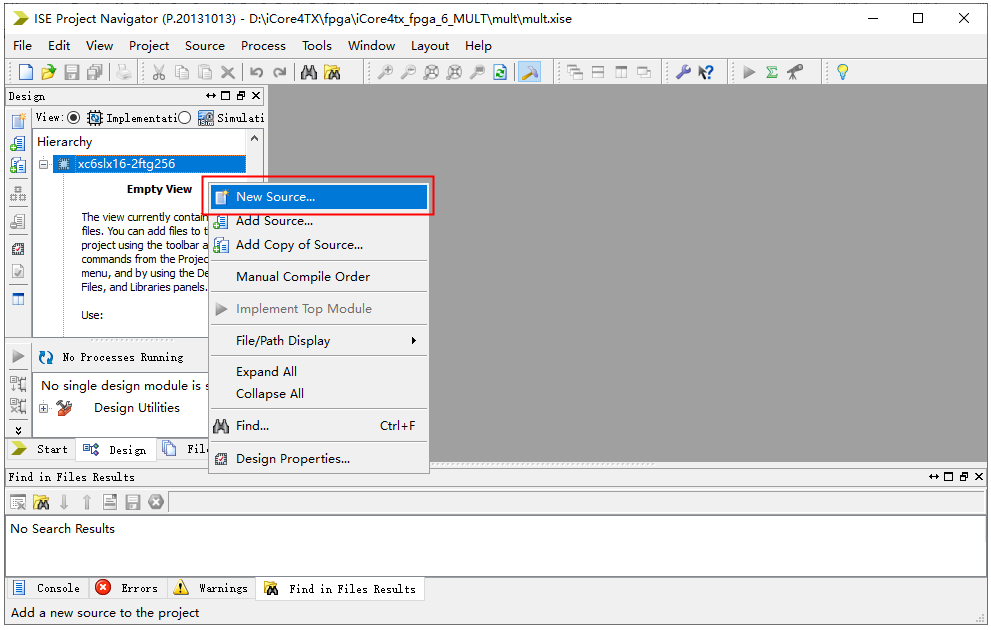

4、添加IP核文件,在工程目录区右键单击,选择New Source…。

4、添加IP核文件,在工程目录区右键单击,选择New Source…。

5、文件类型选择IP(CORE Generator & Architecture Wizard),并给IP核文件命名,点击Next。

5、文件类型选择IP(CORE Generator & Architecture Wizard),并给IP核文件命名,点击Next。

6、点击Math Functions前面的“+”,并选中Multiples下的Multipler,并点击Next,然后点击Finish。

6、点击Math Functions前面的“+”,并选中Multiples下的Multipler,并点击Next,然后点击Finish。

7、进入乘法器IP核设置界面,如下图所示,Multipler Type 选择parallel Multipler,。设置好输入数据的类型和位宽之后点击Next。

7、进入乘法器IP核设置界面,如下图所示,Multipler Type 选择parallel Multipler,。设置好输入数据的类型和位宽之后点击Next。

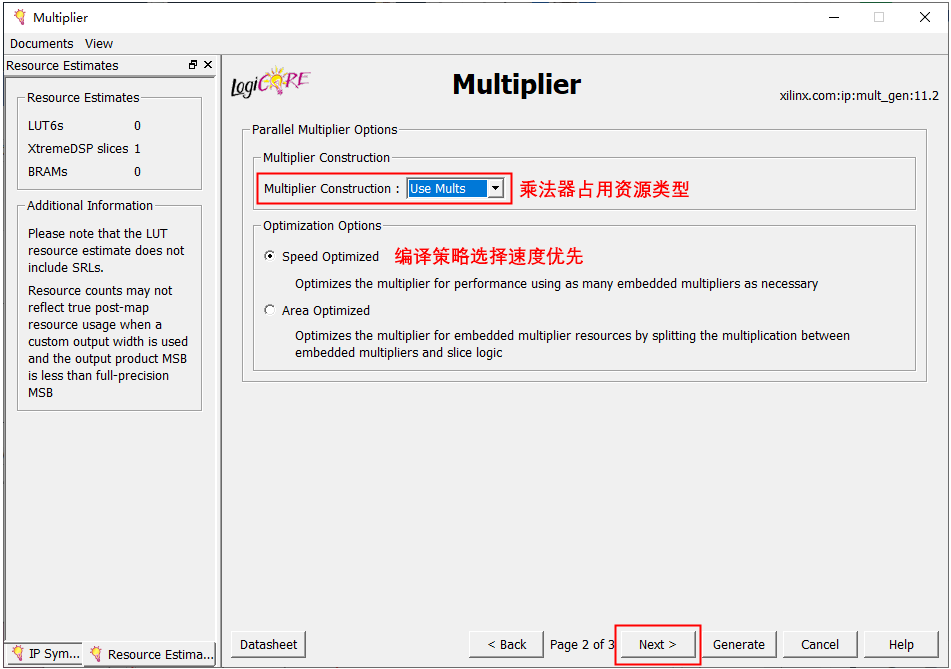

8、设置乘法器IP核占用资源的类型,设置编译优化速度优先还是面积优先;点击Next。

8、设置乘法器IP核占用资源的类型,设置编译优化速度优先还是面积优先;点击Next。

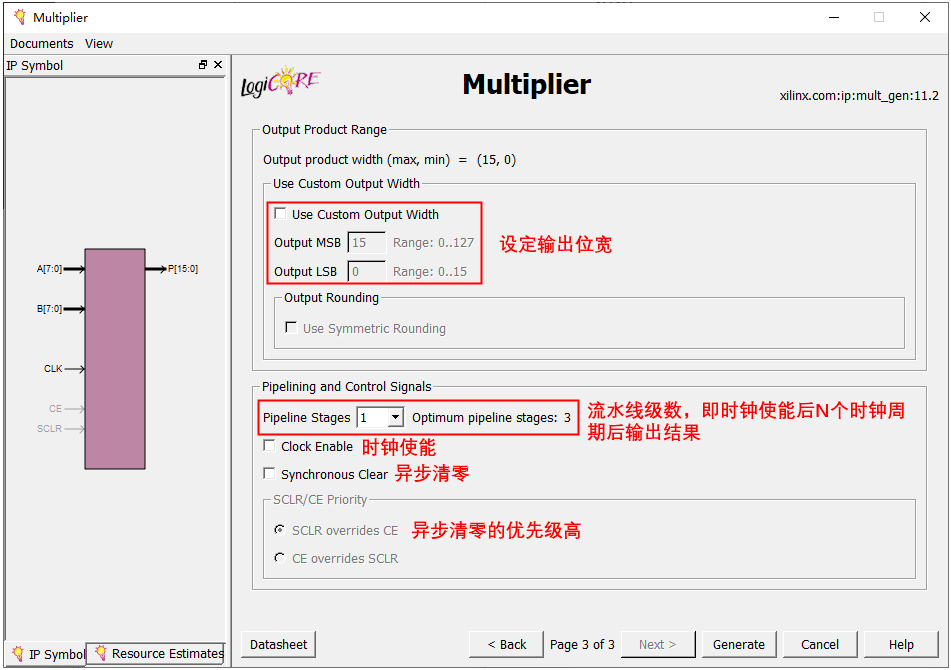

9、选项默认,点击Generate,完成乘法器IP核文件的添加。

9、选项默认,点击Generate,完成乘法器IP核文件的添加。

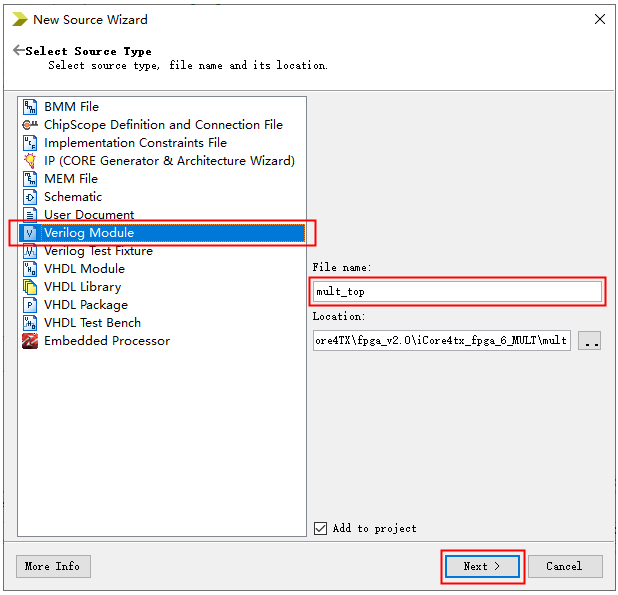

建立顶层文件mult_top.v。

建立顶层文件mult_top.v。

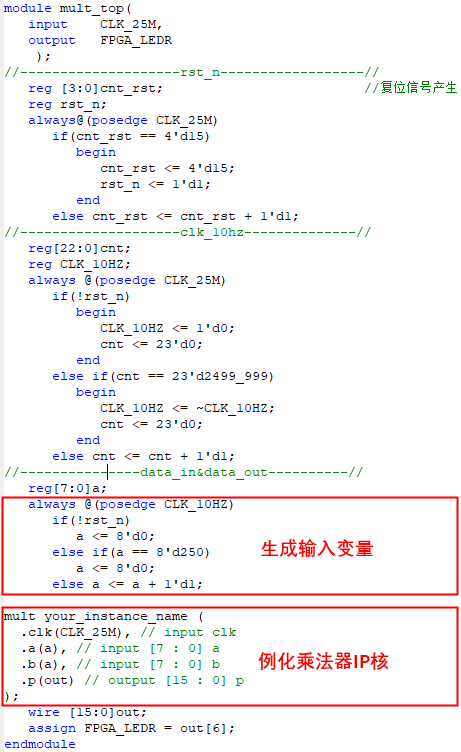

顶层文件中生成输入数据a,并调用乘法器IP核;通过LED灯显示运算结果的变化,代码如下图所示:

顶层文件中生成输入数据a,并调用乘法器IP核;通过LED灯显示运算结果的变化,代码如下图所示:

五、 实验现象

- 打开逻辑分析仪,添加乘法器输入输出波形信号查看波形,可以看到输出数据等于输入数据的乘积(因为采样时钟比较小,逻辑分析仪采样时间稍微有点长,耐心等待一会儿);此外,外部现象表现为红色 LED 闪烁。